QLC 快閃記憶體還沒能大量取代 TLC,而 PLC 也還在草創階段,免驚。

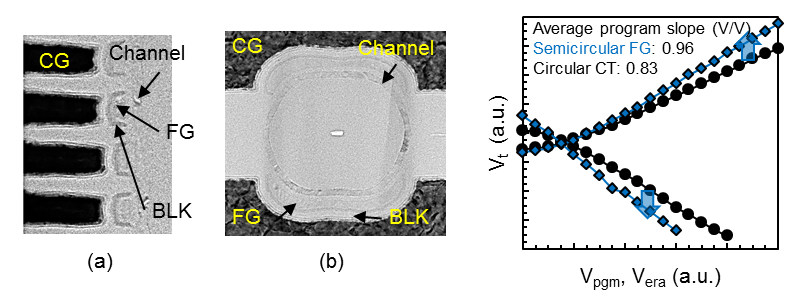

Kioxia(原 Toshiba Memory)稍早於 IEEE International Electron Devices Meeting 上宣布,其 3D NAND 發展邁向新里程碑,已開發出 Twin BiCS Flash 快閃記憶體技術。Twin BiCS Flash 是因應 3D NAND 堆疊發展競爭而生,因為 96 層製品已經開始普遍應用,而 2020 年更將進入 128 層世代。要持續堆疊層數以確保競爭力和獲利,使得製造難度與生產良率更具挑戰性,Kioxia 早早開始尋求突破。

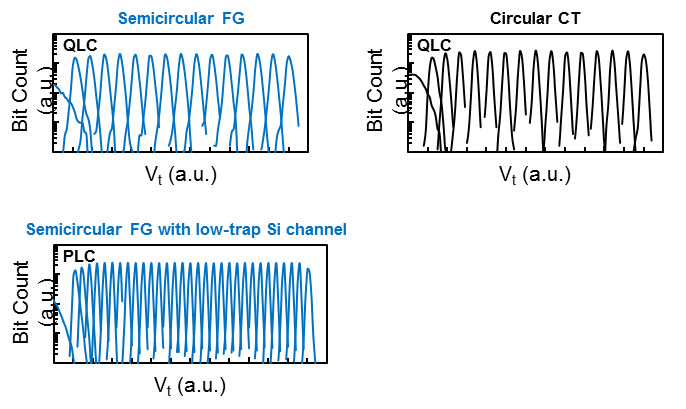

有別於常規的圓形電荷儲存(Charge Trap)架構技術,Kioxia 藉由分割閘極以減小單元尺寸這途徑,新開發出特殊的半圓形浮動閘極(Floating Gate),當前命名為 Twin BiCS Flash。如設計此能夠縮小單元尺寸,同時也可以擁有更多位元,兩者都能夠實現儲存密度提升。Kioxia 指出經實證,Twin BiCS Flash 除了有利於 QLC(4bit / cell)運用,更是邁向 PLC(5bit / cell)發展可行的候選方案。