英特爾目標在封裝達成超過10倍的密度提升和30%至50%的邏輯尺寸微縮改善、並超越傳統矽電晶體。

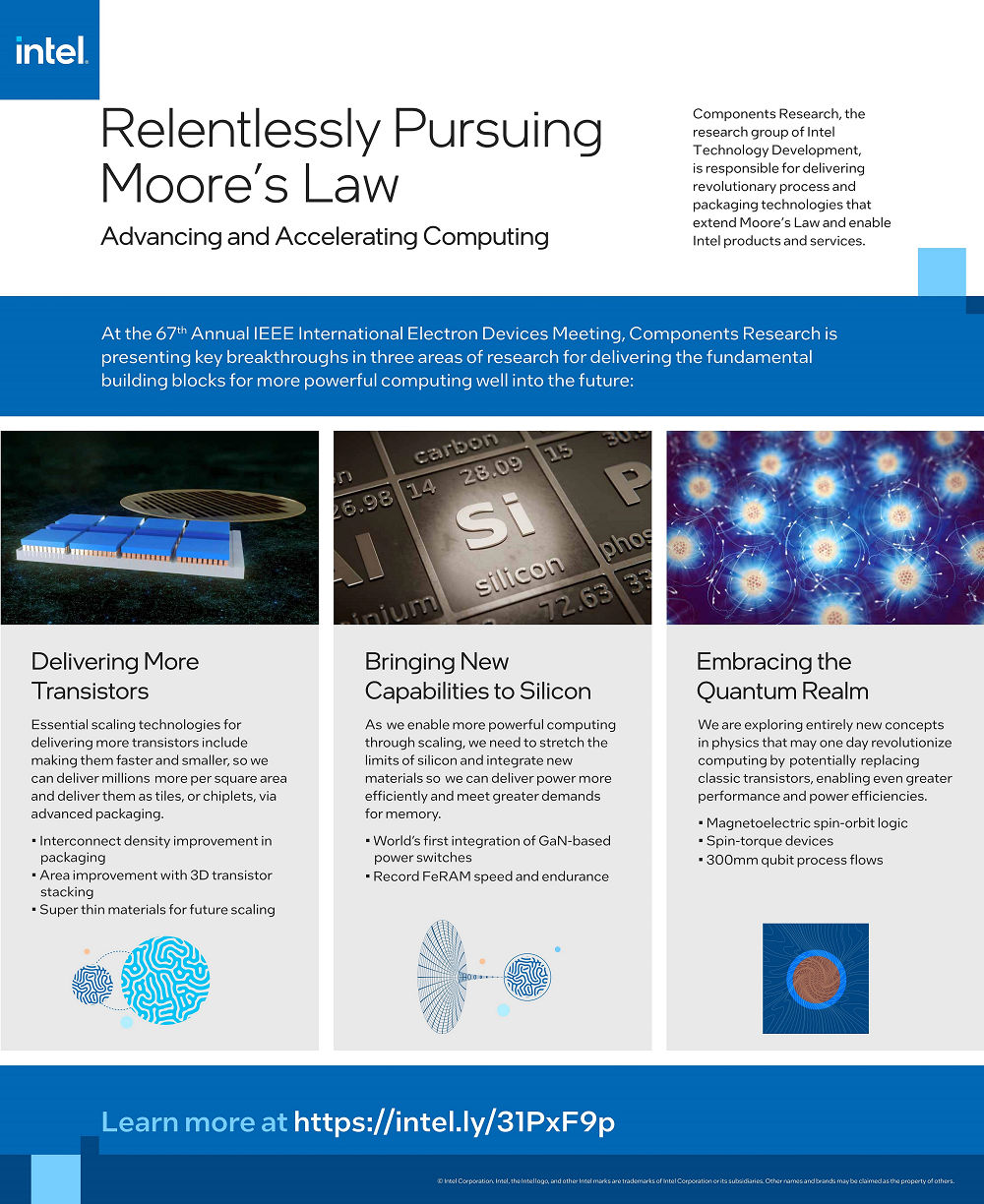

在不斷追尋摩爾定律的道路上,英特爾揭曉其關鍵封裝、電晶體和量子物理等根本性突破,推進和加速運算進入下個十年。於IEEE International Electron Devices Meeting(IEDM)2021,英特爾概要地論述採用混合鍵合(hybrid bonding)技術,在封裝中提升超過10倍互連密度的過程、電晶體微縮達成30%至50%的面積改善、新電源和新記憶體技術的重大突破,以及未來某個時刻將徹底顛覆運算的新物理概念。

「在英特爾心中,推進摩爾定律所需的研究和創新永不停歇。我們的元件研究事業群於IEDM 2021分享關鍵研究突破,帶來革命性的製程和封裝技術,滿足我們產業和社會所仰賴且永遠不會滿足的需求。這是我們最棒的科學家和工程師勤勉不懈的工作成果,他們將走在創新最前線,繼續為延續摩爾定律而努力。」– Robert Chau,英特爾資深院士暨元件研究經理。

為何重要:摩爾定律已經隨著運算創新,滿足從大型電腦至行動電話每個科技世代的需求,這條演化之路隨著我們進入無限資料和人工智慧的新運算時代得以延續。

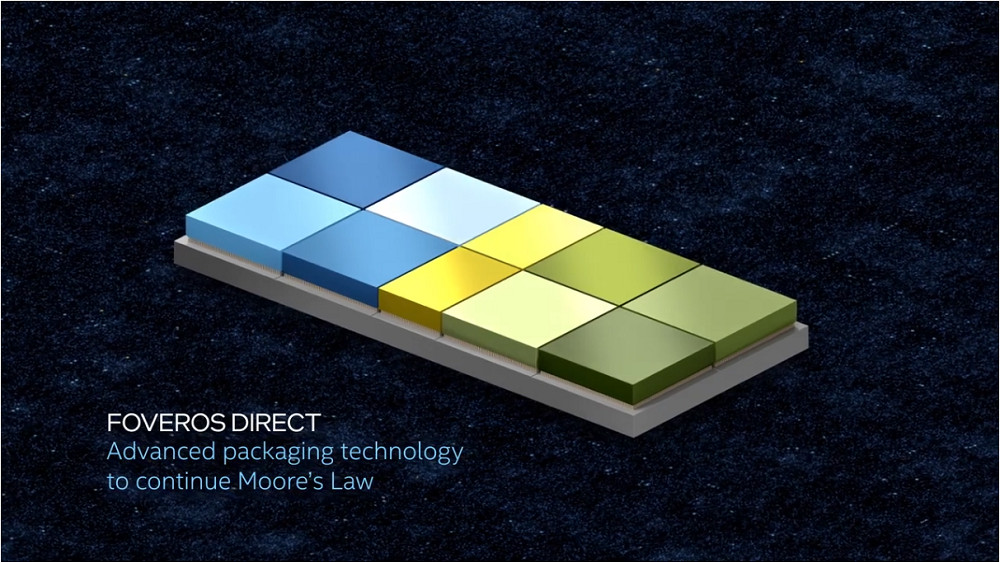

持續不斷地創新為摩爾定律的基石。英特爾的元件研究事業群致力於橫跨3個關鍵領域創新:提供更多電晶體的必要微縮技術、提升電源和記憶體的新矽功能、探索新物理概念以便革命性地改變世界運算的方式。藉由元件研究的工作,許多創新已打破先前摩爾定律的障礙,並實際應用於當今產品之中-包含應變矽、Hi-K金屬閘極、FinFET、RibbonFET,以及包含EMIB、Foveros Direct在內的封裝創新。

如何做到:在IEDM 2021揭曉的突破,表示英特爾有望在2025之後,藉由下列3項領域的探索,繼續推進和汲取摩爾定律優勢:

- 英特爾正追尋基本微縮技術的重要研究,能夠在未來的產品之中提供更多的電晶體:

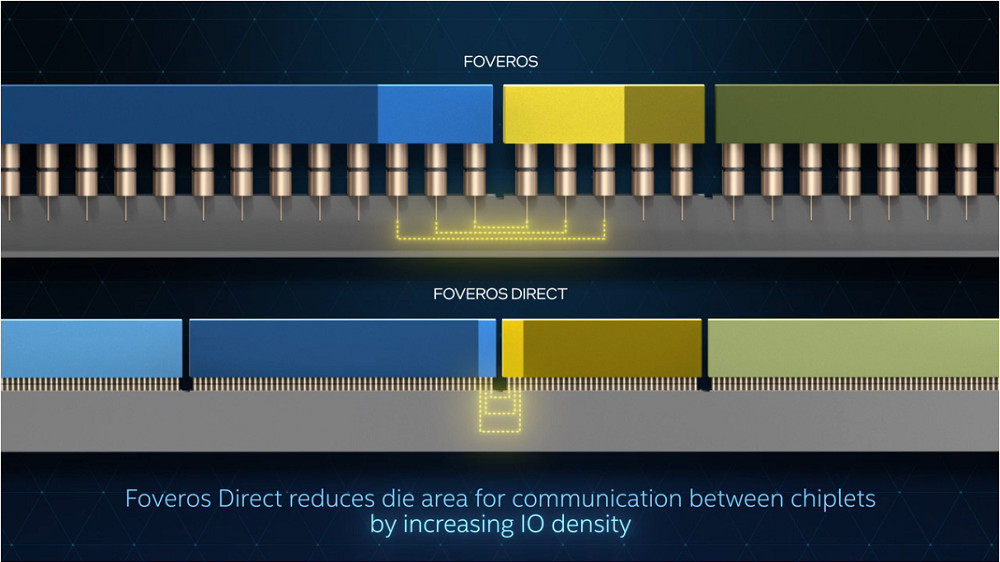

- 公司研究人員為混合鍵合互連設計、製程和組裝挑戰提出解決方案綱要,展望在封裝中超過10倍的互連密度改善。於7月舉行的Intel Accelerated活動,英特爾宣布導入Foveros Direct的計畫,達成10微米以下的凸點間距,為3D封裝提供一個量級的互連密度提升。為了讓生態系能夠從先進封裝當中受益,英特爾同樣也呼籲建立業界新標準和測試步驟,促成混合鍵合小晶片(chiplet)生態系。

- 展望環繞式閘極(gate-all-around)RibbonFET,英特爾正在透過堆疊多個(CMOS)電晶體的方法,掌握即將到來的後FinFET時代,藉由在每平方毫米放入更多的電晶體,目標達成最高30%至50%的邏輯微縮改善,繼續推進摩爾定律。

- 英特爾同時透過前瞻性研究,為摩爾定律鋪設前進埃(angstrom)時代的道路,展示僅有數個原子厚度的新型材料,如何能夠做出克服傳統矽通道限制的電晶體,讓每個晶片面積上增加數百萬個電晶體,為下個十年提供更為強大的運算。

- 英特爾同時為矽帶來新功能:

- 在300mm晶圓上,達成全球首創整合以氮化鎵(GaN)為基礎的電源開關和以矽為基礎的CMOS,推進更有效率的電源技術。為CPU提供低損失、高速的電源供應,並同時縮減主機板元件和空間。

- 另一項進展為英特爾使用新型鐵電材料,達成領先業界、低延遲讀寫能力,且有可能成為次世代嵌入式DRAM技術,提供更多的記憶體資源,解決從遊戲到AI等運算應用日益複雜的問題。

- 英特爾正在追尋以矽電晶體為基礎的量子運算所帶來的強勁效能,以及與新型室溫裝置搭配運作,擁有巨量能源效率運算的全新開關。在未來,這些採用全新物理概念的揭示,可能會取代傳統MOSFET:

- 於IEDM 2021,英特爾展示於室溫運作的全球首款實驗性磁電自旋軌道(magnetoelectric spin-orbit、MESO)邏輯裝置實作,顯示出基於開關奈米規模磁鐵的新型電晶體可製造性的潛力。

- 英特爾和IMEC在自旋電子材料研究取得進展,將裝置整合研究更進一步帶往實現全功能自旋轉距(spin-torque)裝置。

- 英特爾還展出與CMOS生產製造相容,用來實現可擴展量子運算的完整300mm量子位元製程流程,並確定未來研究的下一步。

關於元件研究:元件研究(Components Research)為英特爾技術開發的研究事業群,負責提供延續摩爾定律的革命性製程和封裝技術選項,並啟發英特爾產品與服務。它持續與公司的事業單位合作預測未來需求,並偕同美國政府研究實驗室和產業聯盟,再到大學研究團體和供應商,維持英特爾研發流程的完整性。