揭露兩款x86 CPU核心新架構、兩款資料中心SoC、兩款獨立式GPU,並為PC客戶端打造革命性的多核性能混合架構。

英特爾公司舉行架構日,揭曉英特爾架構最為重大的世代轉換。重點包括:

- 首次深入介紹,英特爾首款具備兩個全新x86核心世代的混合式架構-Alder Lake,以及智慧型Intel® Thread Director工作負載排程器;

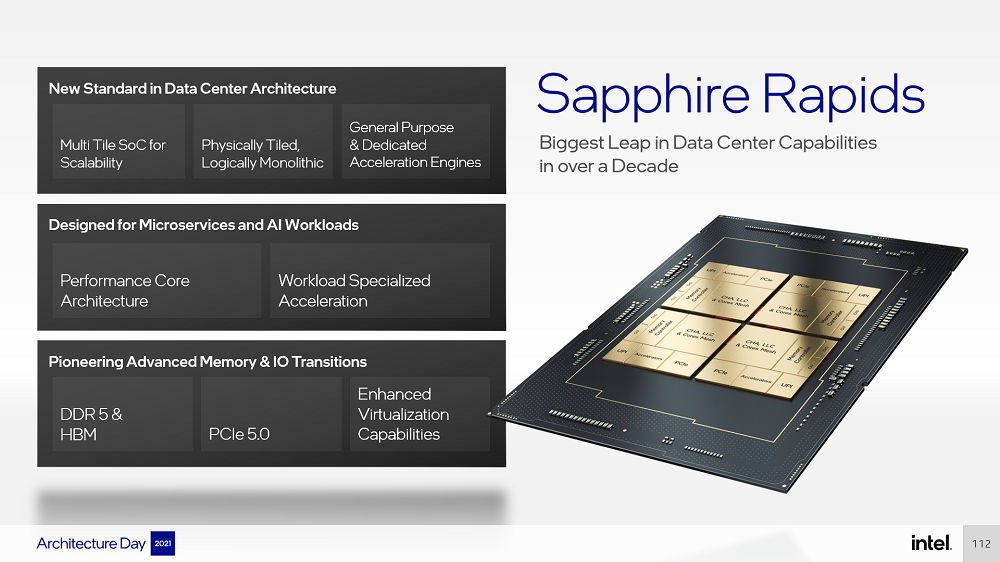

- Sapphire Rapids,英特爾為資料中心所設下的新標準,架構上結合了我們的效能核心以及眾多加速器引擎;

- 英特爾全新的獨立遊戲圖形處理單元(GPU)架構;

- 英特爾新款基礎設施處理器(IPU);

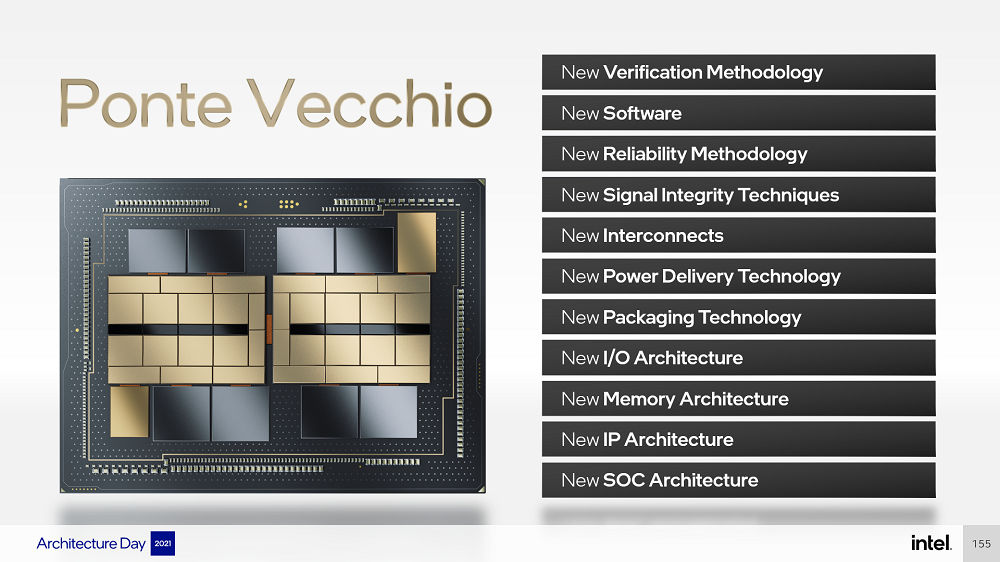

- Ponte Vecchio,英特爾有史以來最高運算密度的資料中心GPU架構。

這些架構上的突破為英特爾下個世代的領先產品奠定基礎,Alder Lake不久即將與大家見面。隨著從桌面到資料中心的工作負載,變得更大、更多、更複雜和更多元,架構日所揭曉的技術突破更加顯現出優秀的架構將如何滿足更多運算效能的迫切需求。

效率核心(Efficient-core):從低功耗行動應用至多核心微服務,這是一款滿足我們客戶廣泛運算需求,高度可擴充的x86微架構。相較於英特爾最為豐富的Skylake微架構,效率核心於同樣功耗下可提供高出40%的效能,或是在相同效能的前提下,降低40%的功耗1。多核心處理下,4個效率核心相較以4條執行緒方式運作的Skylake雙核心,能夠提供多出80%的效能並降低功耗,或是減少80%的功耗並維持相同的效能1。

效能核心(Performance-core):這款x86核心不僅是英特爾迄今所打造的最高效能CPU核心,同時也為驅動下個運算十年,在CPU架構上跨出重要一步。其設計主旨為更寬、更深、更智慧,達成更好的平行作業、提升執行平行度、降低延遲必提升通用運算效能。其同樣協助支援具備眾多資料與大量程式碼的應用程式。效能核心相較我們目前第11代Intel® Core™架構(Cypress Cove核心),於相同運作頻率之下,在寬廣及多樣的工作負載能夠提供約19%的改善1。

針對資料中心處理器以及機器學習不斷發展的趨勢,效能核心導入專用硬體,包含英特爾全新的Advanced Matrix Extensions(AMX),以效能提升一個量級的方式執行矩陣乘法運算-人工智慧加速將近8倍1。此架構開發時考量軟體易用性,汲取x86程式開發模型優勢。

Intel Thread Director:英特爾針對排程器的獨到設計,為確保效率核心和效能核心工作無縫接軌而開發,自開始即動態且智慧地指派工作,讓真實世界的系統效能最大化與效率最佳化。透過內建於核心內部的智慧,Intel Thread Director與作業系統搭配得天衣無縫,在對的時間點將執行中的工作移往正確的核心。

Alder Lake:重塑多核心架構,Alder Laker將是英特爾具備全新Intel Thread Director的首款高效能混合式架構。以高效率核心和高效能核心相互結合作為號召,這是英特爾最為智慧的PC客戶端SoC架構,可從超輕薄行動市場一路延伸至桌面系統,並以多項領先業界的I/O與記憶體引領產業轉型。基於Alder Lake的產品將於今年開始出貨。

Xe HPG 和 Alchemist SoC:針對玩家級遊戲效能和內容創作工作負載而設計的一款全新獨立式圖形微架構。Xe HPG微架構具備新款Xe-core,是款專注於運算的可程式化和可擴充的元件,並全面支援DirectX 12 Ultimate。位於Xe-cores內部的新款矩陣引擎(也就是Xe Matrix eXtensions、XMX),能夠加速如XeSS的AI工作負載,XeSS更是一款能夠同時達成高效能與高度逼真遊戲的新穎畫面提升(upscaling)技術。以Xe HPG打造的Alchemist SoC(先前代號DG2)將使用全新Intel® Arc™品牌,於2022年第一季現身,並以TSMC N6製程打造。

Sapphire Rapids:結合英特爾的效能核心與全新加速器引擎,Sapphire Rapids為下一世代的資料中心處理器設下新標準。平舖的(tiled)、模組化的SoC架構位於Sapphire Rapids中心,提供驚人擴充性的同時,依舊保持單一CPU晶片介面所享有的優勢,這要歸功於英特爾的EMIB封裝技術與先進的mesh架構。

基礎設施處理器(IPU):Mount Evans是英特爾首款以ASIC為基礎的IPU,還有以FPGA為基礎的全新IPU參考平台Oak Springs Canyon。透過以英特爾IPU為基礎的架構,雲端服務提供者(CSP)藉由從CPU卸載基礎設施任務至IPU,可以最大化資料中心收益。卸載基礎設施任務至IPU,讓雲端服務提供者能夠將他們的伺服器CPU 100%提供給客戶租用。

Xe HPC、Ponte Vecchio:Ponte Vecchio利用多個先進半導體製程優勢、英特爾革命性的EMIB多晶片互連技術,以及英特爾的Foveros 3D封裝,Ponte Vecchio成為英特爾打造過最為複雜的SoC,亦是英特爾IDM 2.0策略的絕佳範例。運算晶片(Compute Tiles)將採用TSMC N5製程;基底晶片(Base Tile)則是使用Intel 7製程;連結晶片(Xe Link Tile)將採用TSMC N7製程。透過這款產品,我們實現猶如登月任務般艱難的專案,這個千億個電晶體的裝置可提供領先業界的浮點運算效能與運算密度,加速AI、HPC和先進分析工作負載。早先英特爾展示過的Ponte Vecchio晶片已可表現出領先效能,我們A0版晶片已經能夠提供超過45 TFLOPS的FP32吞吐量,大於5 TBps的記憶體組織結構頻寬,以及突破2 TBps的連接頻寬1。如同我們的Xe架構,Ponte Vecchio同樣由開放、以標準為基礎、跨架構、跨供應商的統一軟體堆疊oneAPI所支援。

回首過去一年,全球以科技來進行溝通、工作、遊憩,並且對抗疫情。事實證明,強大的運算能力相當重要。展望未來,我們面對著大量運算需求-到了2025年可能需要1,000倍。4年之內成長1,000倍,相當於摩爾定律的5次方。

英特爾CEO Pat Gelsinger(基辛格)提到:「我們正面臨望之生畏的運算挑戰,這些挑戰只能夠透過革命性的架構和平台去解決……英特爾亟富才華的架構師和工程師們,讓這些技術成為可能。」世界正仰賴著架構師和工程師們解決最為困難的運算難題,以豐富人們的生活。這正是英特爾為何加速執行我們的策略,因為我們的策略與執行正以極快的步伐,加速滿足這些需求。