傳輸速率再一次翻倍,PCIe 6.0 x16 通道配置頻寬高達 128GB/s。

因應各式應用對於頻寬的需求無止境,PCIe 規範領導制定官方組織 PCI-SIG,所研擬 PCIe 6.0 規範草案於日前更新至 0.9 版,而這也是最後一個草案版本,意味正式版本的發布時間點不遠了。

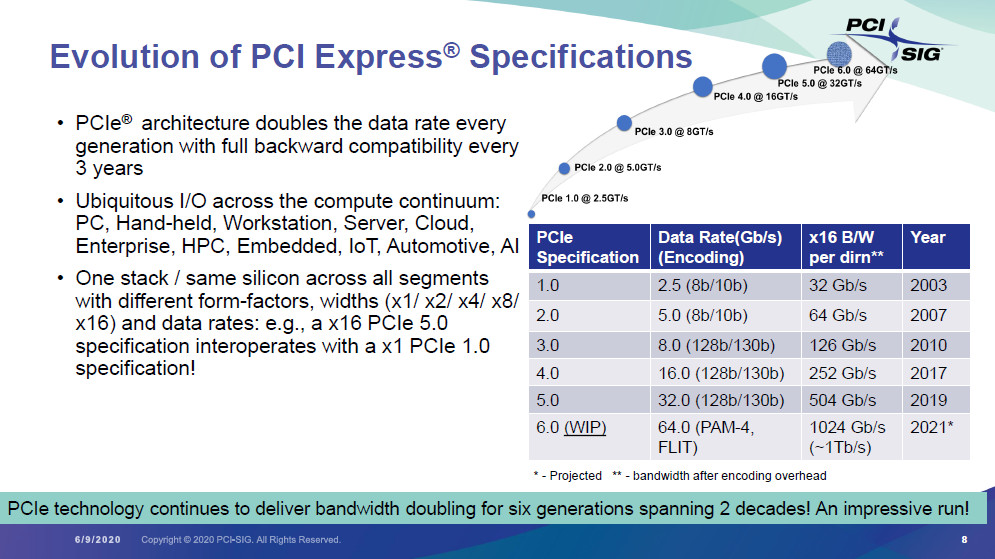

如同過往,PCI-SIG 將 PCIe 6.0 傳輸速率提高一倍設為目標,同時也保留向上、下相容性。PCIe 6.0 規範 0.9 版最終草案發布之後,PCI-SIG 將邀集協會成員進行專利技術等審查作業,預估不會再更動 PCIe 6.0 規範草案內的功能、細節等部分。

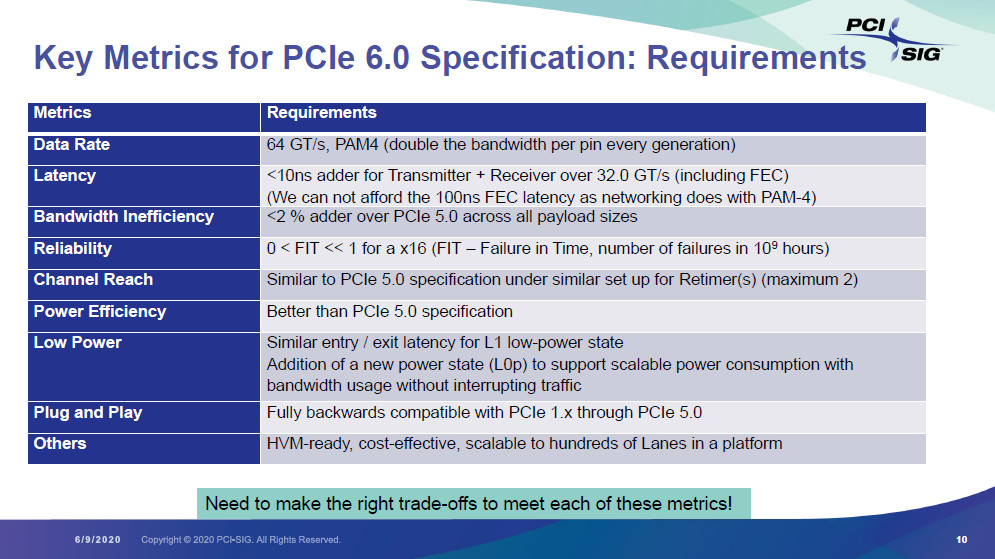

為達成這次改朝換代目的,PCIe 6.0 規範特性有一些重大轉變,像是導入 PAM-4(Pulse Amplitude Modulation with 4 levels)與 FLIT(Flow Control Unit)編碼、FEC(Forward Error Correction )低延遲錯誤檢測和糾正等設計。

這是自 PCIe 3.0 開始導入 128b/130b 編碼之後,再一次的架構設計重大轉變,PCI-SIG 成功使 PCIe 6.0 傳輸速率,由 PCIe 5.0 的 32GT/s 倍增至 64GT/s,也就是說 PCIe 6.0 x16 通道配置頻寬將可以達到趨近 128GB/s 之譜。

屬於未來式的 PCIe 6.0,相關產品設計製造成本可能會墊高不少,因此被導入個人電腦平台的速度不好說。現階段而言,如果 Intel 的計畫沒有途中生變,那麼個人電腦平台在 1 個月之後,將首度擁有 PCIe 5.0 匯流排介面,先看它會如何普及吧。