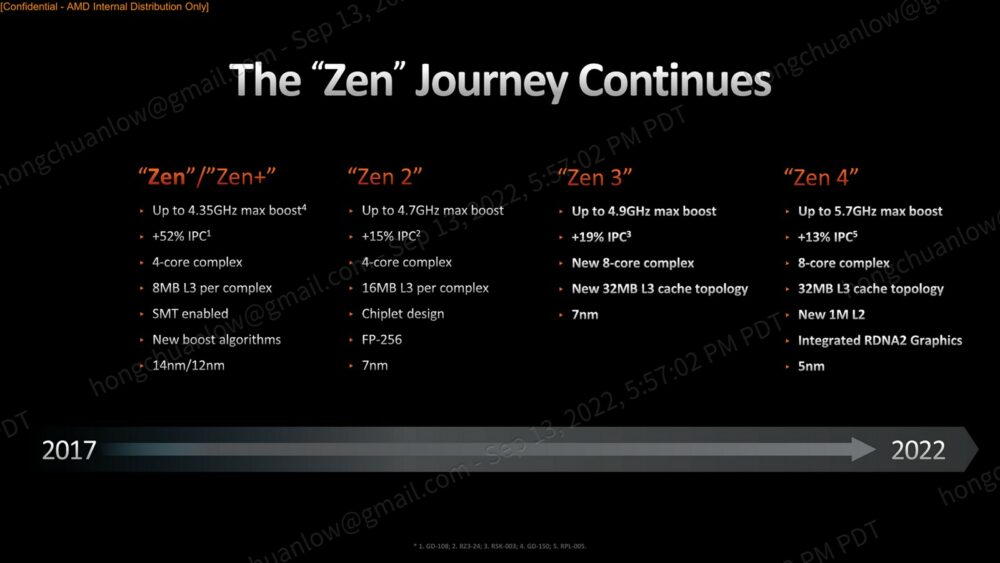

外行看熱鬧,內行看門道。就讓我們一起來觀察這次轉換至全新 AM5 平台的 Zen 4 微架構及其 SoC 設計,相較 Zen 3 是如何達成提升 IPC 13% 的效能新高。

CCD、IOD 全面更新

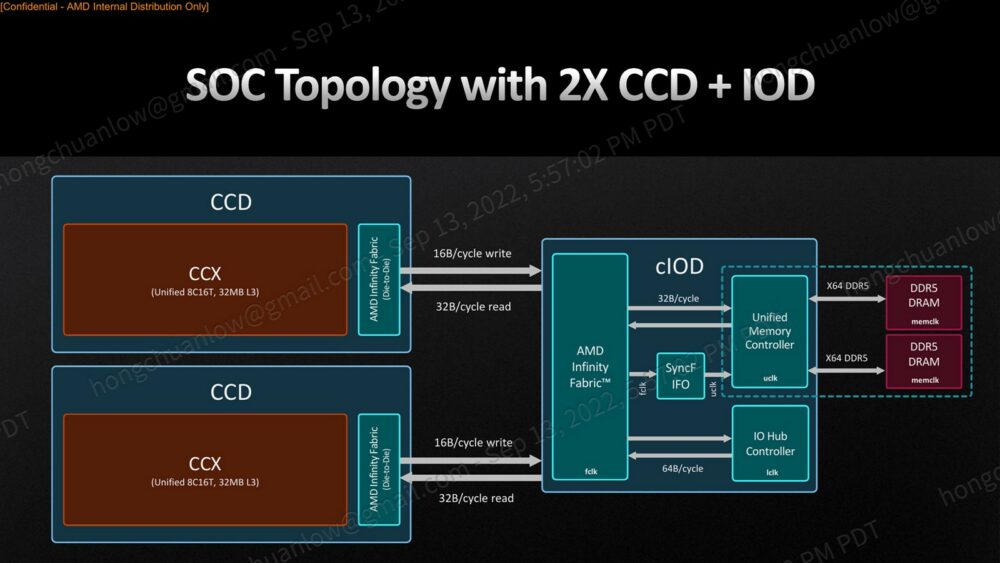

目前 AMD 多款處理器已導入小晶片 chiplet 設計,可以自由地組合針對不同市場、效能的產品。這一次在消費級桌上型電腦市場首發的 Ryzen 7000 桌上型處理器系列(代號 Raphael),繼續採用 CCD+cIOD(client IOD)設計,分別採用 TSMC N5 以及 N6 製程。

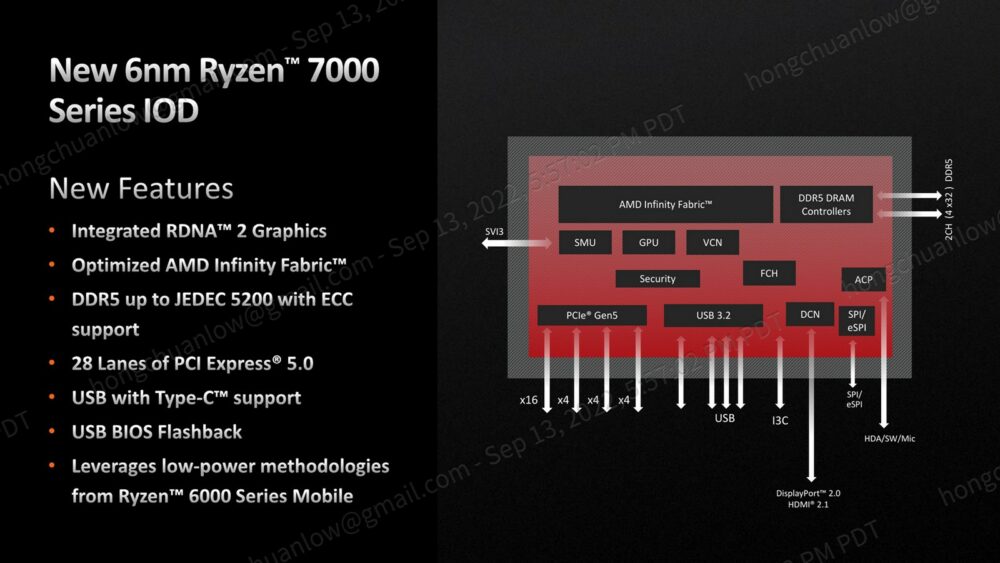

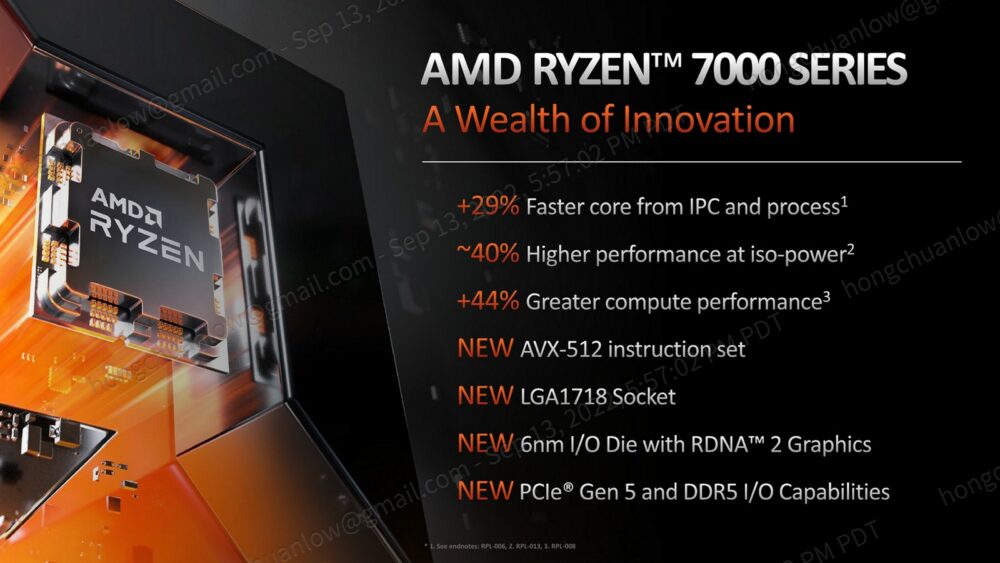

Ryzen 7000 桌上型處理器系列除了 CCD 內部更新至 Zen 4 微架構之外,其 cIOD 也因為轉換至 AM5 新平台之故,新增 DDR5 記憶體和 PCIe 5.0 支援性,更重要的是內建 RDNA 2 架構的繪圖顯示功能,補完過去在商業市場尚待拼湊完成的產品線。

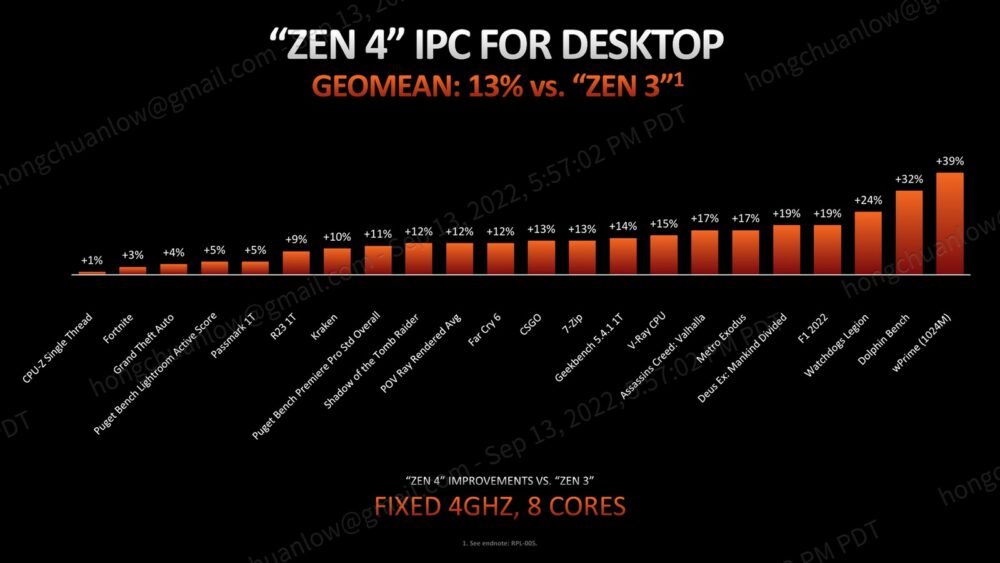

根據 AMD 官方提供的資料,在同樣的 4GHz 運作時脈、8 核心比較基礎之下,Zen 4 微架構相較於前一世代 Zen 3 微架構,其 IPC(Instructions Per Clock/Cycle)於多款測試軟體的幾何平均效能提升了 13%。

▼AM5 平台全面升級,處理器微架構升級成 Zen 4,cIOD 也增添繪圖顯示功能,更全面轉入 DDR5 記憶體和 PCIe 5.0 規格。

▼於相同的 4GHz 運作時脈、8 核心比較基礎之下,Zen 4 微架構相較於 Zen 3 微架構的 IPC 幾何平均提升了 13%。

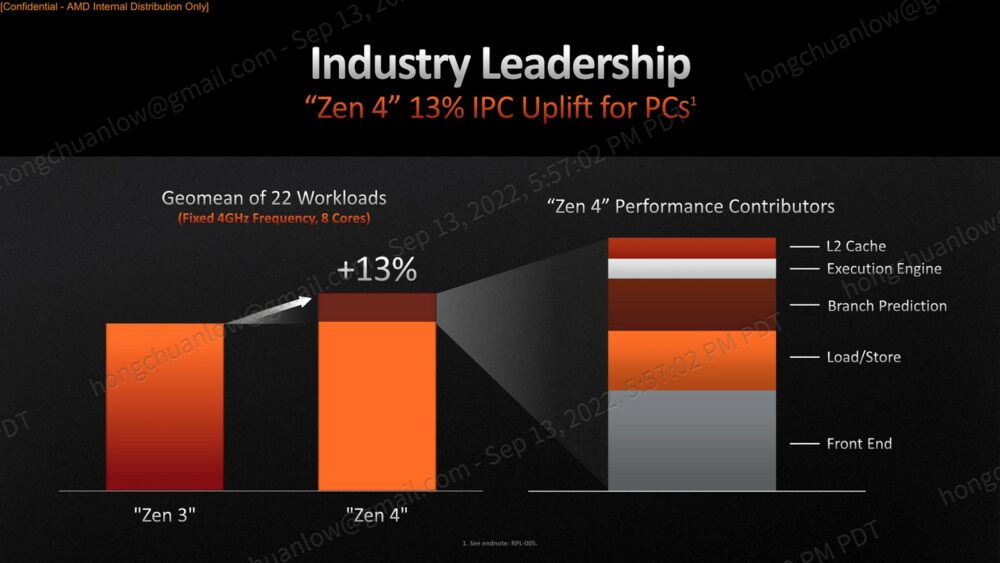

Zen 4 微架構新增 AVX-512、VNNI、BF16 支援性

由於 Zen 4 是從 Zen 3 微架構修改而來,若是讀者比較不熟悉這方面的資訊,建議可以搭配上方的延伸閱讀一同服用、效果更佳。整體而言,Zen 4 IPC 提升幅度,貢獻最大的是處理器核心前端的變化,接著是載入∕儲存單元以及分支預測,執行單元與雙倍大(1MB vs. 512KB)的 L2 快取則僅占一小部分。

▼ 相較於 Zen 3,Zen 4 微架構的前端改良對於效能提升貢獻最大,其次是載入 ∕ 儲存單元以及分支預測。

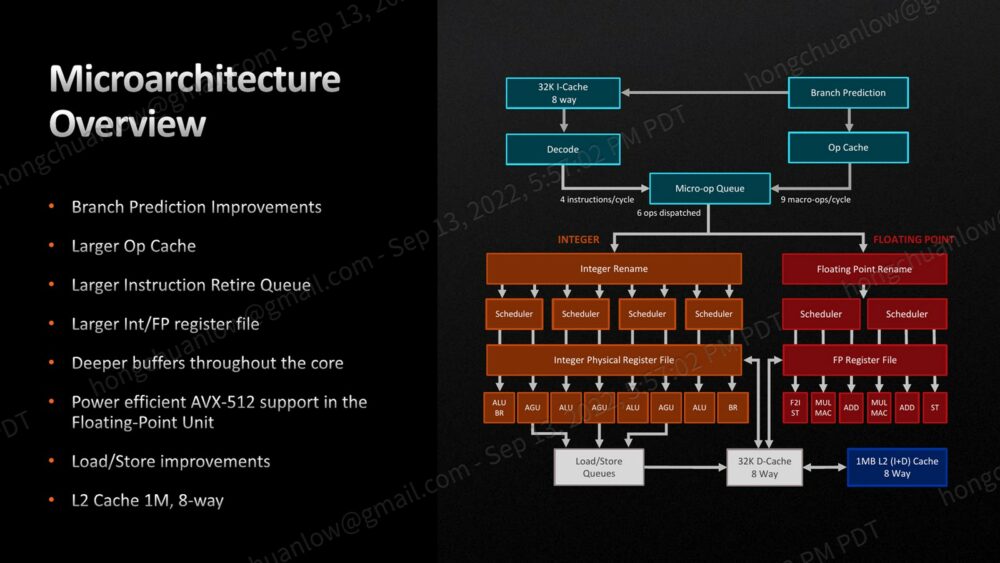

▼ Zen 4 微架構的改良包含分支預測、更大的微指令快取、更大的指令 retire 佇列、更多的整數 ∕ 浮點數暫存器數量、加深核心整體的緩衝區、載入 ∕ 儲存單元、1MB L2 快取,當然還有新增 AVX-512 指令集。

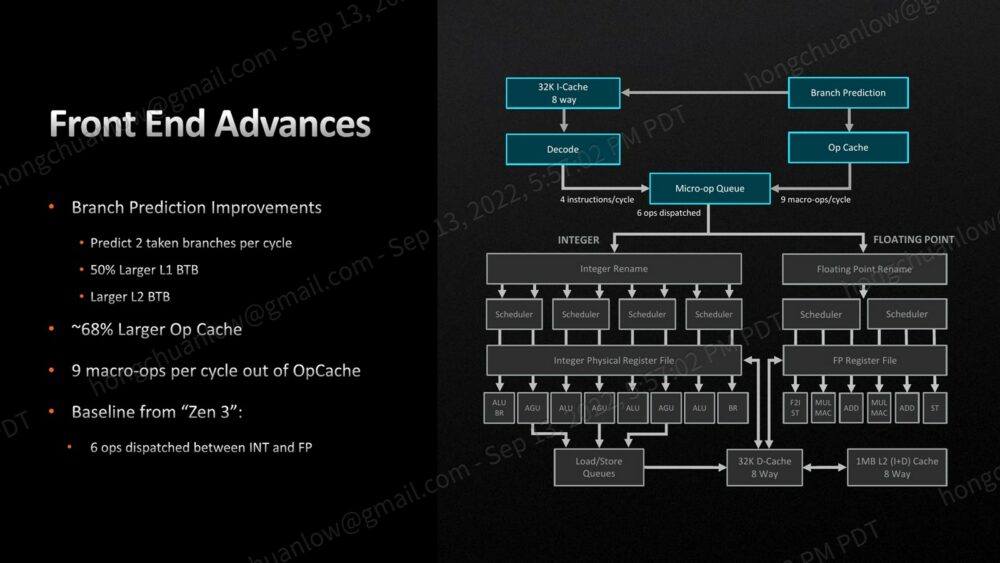

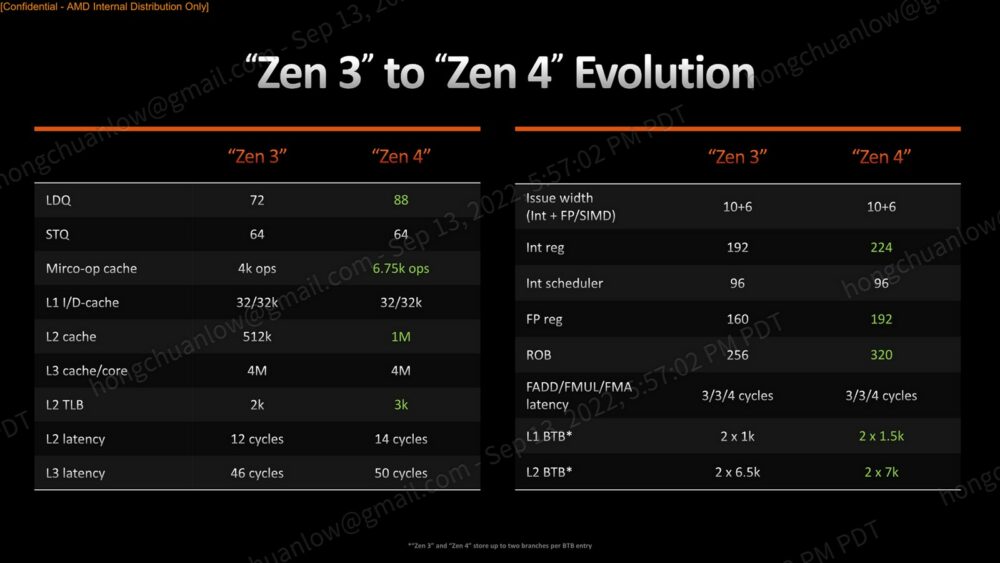

前端分支預測、指令解碼、微指令快取等各個部分,分支預測改良包含每週期可預測 2 個跳轉分支、L1 BTB(Branch Target Buffer)增大 50% 達 1.5k 條目(Zen 3 和 Zen 4 每個條目均可儲存 2 個分支)、L2 BTB 則從 6.5k 略微提升至 7k。微指令快取(micro-op cache)則從 Zen 3 的 4k 條目提升約 68% 來到 Zen 4 的 6.75k 條目,每時脈週期也多出 1 條巨集指令(共 9 條巨集指令)可從該快取傳出至微指令佇列,解碼器每時脈週期則是依舊可以解出 4 條指令至微指令佇列當中。至於微指令佇列每時脈週期可配發的數量不變,整數加上浮點數同樣是 6 條指令。

▼ Zen 4 前端部分相較於 Zen 3 變化較大,BTB 和微指令快取均有程度不一的數量提升。

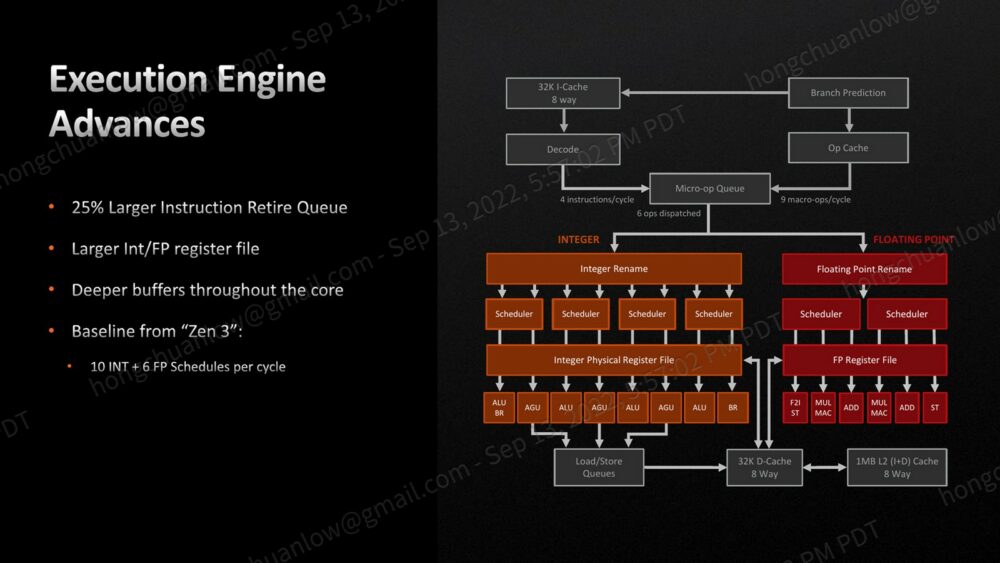

相較於前端的變化,各個執行單元反而沒有什麼更動,Zen 4 整數、浮點數執行單元數量相同,每時脈週期能夠 issue 的指令數量依舊維持 10 + 6(整數 + 浮點數)。幅度較大的改變現蹤於暫存器數量和 ROB(Re-Order Buffer),整數暫存器從 192 個提升至 224 個,浮點數暫存器從 160 個提升至 192 個,ROB 則是從 256 條目提升至 320 條目。

▼ Zen 4 執行單元沒有太大的變動,主要是提升暫存器和 ROB 數量。

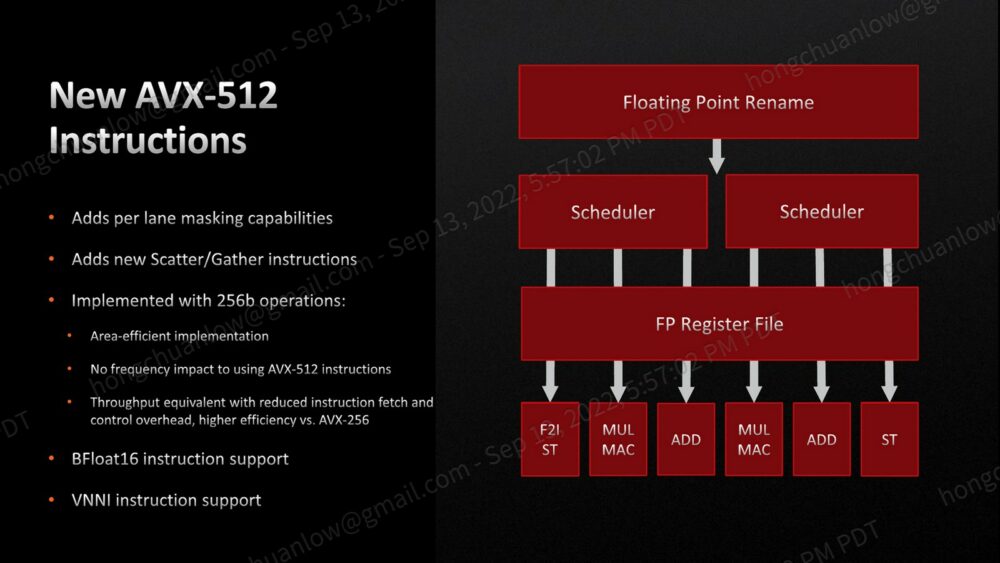

有趣的是,AMD 這次又將過去的手法套用在 Zen 4 身上。不若 Intel 微架構執行 AVX-512 系列指令時,其執行通道確確實實達 512 bit,Zen 4 的浮點數執行單元寬度僅有 256 bit。如同先前工程機械類、Zen 微架構以 128 bit 浮點單元執行 256 bit AVX / AVX2 指令時一樣,需要將單一 AVX-512 指令拆成 2 個微指令。

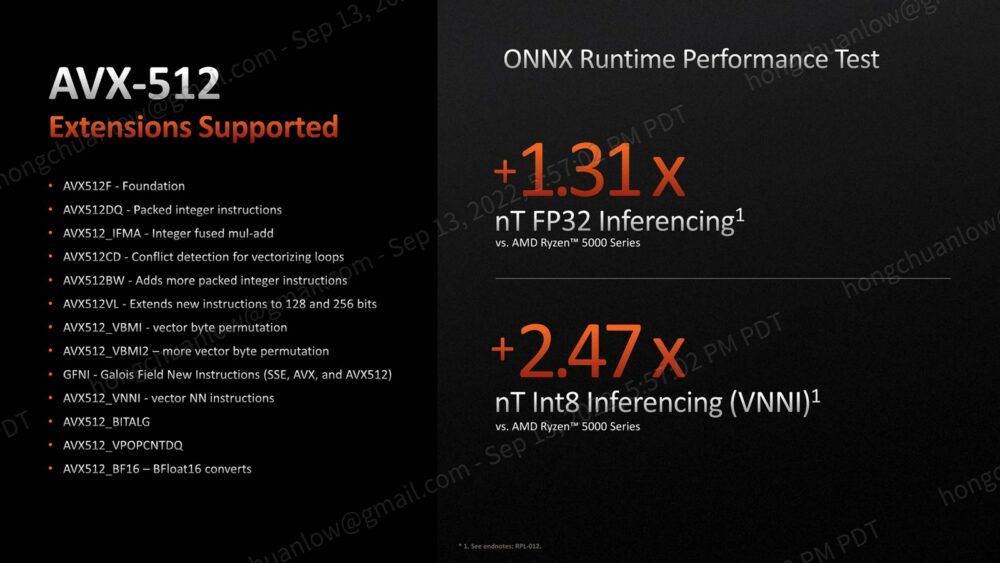

AMD 表示這種作法除了能夠最佳化晶片面積之外,也可以避免執行 AVX-512 指令時的時脈下降狀況。此外,Zen 4 也支援 AVX-512 VNNI 和 BF16,前者主要用於 AI 模型推論,將多個 8 bit 或是 16 bit 整數串成 512 bit,提升卷積神經網路常用的 MAC(Multiply Accumulate)速度;後者則是將 FP32 的 1 位符號數 +8 位指數 +23 位小數的結構,將小數砍到只剩 7 位,得到與 FP32 範圍相同、精度較差的 BF16,同樣也是用來加速 AI 運算的速度。

▼ AMD Zen 4 提供 AVX-512 一系列指令集的支援性,包含可加速 AI 應用的 AVX-512 VNNI 和 BF16,不過其浮點數執行通道寬度僅有 256 bit。

▼ Zen 4 支援 AVX-512 延伸指令集一覽,AMD 表示多執行緒 FP32 的推論效能提升 1.32 倍,多執行緒 INT8 的推論效能更能夠提升 2.47 倍。

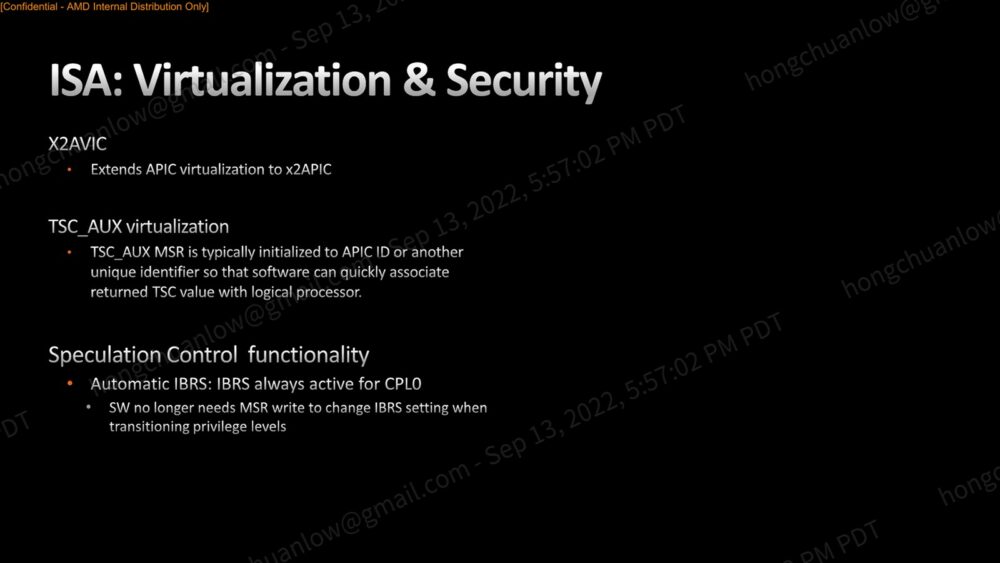

▼ Zen 4 也新增有關虛擬化和安全性方面的指令。

雙倍大 L2 快取、Outstanding Miss 數量提升

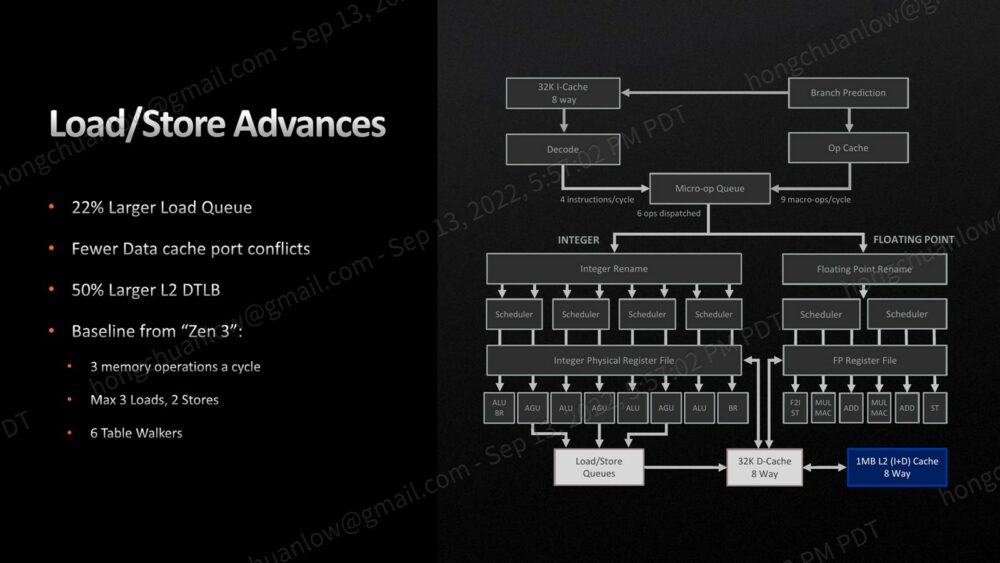

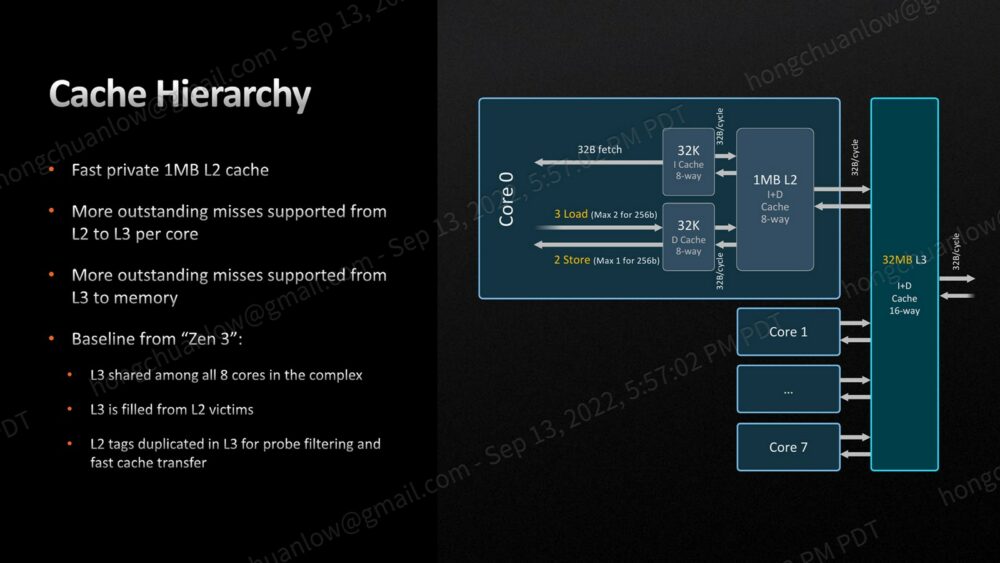

由於浮點數執行單元的寬度最寬仍舊是 256bit,以此載入∕儲存單元也就沒有倍增至 512bit 的必要。L1 資料快取仍舊是每週期載入 3 筆(256bit 時降為 2 筆)∕寫入 2 筆(256bit 時降為 1 筆)資料,L2 快取倍增為 1MB,L3 快取則維持每個 CCD 8 核心共享 32MB。

相較於 Zen 3,Zen 4 微架構的 L2 快取至 L3 快取、L3 快取至記憶體的 Outstanding Miss 數量有所提升,但 AMD 公開資料並未提及究竟多出多少?其餘像是 L3 快取是 victim cache 結構,L2 快取的 tag 複製至 L3 快取之中,供 probe filtering 與加速快取傳輸之用,Zen 4 均繼承 Zen 3 設計。

▼ Zen 4 載入∕儲存單元的載入佇列從 72 個提升至 88 個,儲存佇列則是維持 64 個不變,L2 快取的資料 TLB 則從 2k 條目提升 50% 至 3k 條目。

▼ 除了 L2 快取從 512KB 升級至 1MB 之外,其餘快取階層、每時脈週期傳輸量均沿用 Zen 3 設計,但是 L2/L3 快取 Outstanding Miss 數量有所提升。

▼ Zen 4 相對於 Zen 3 各項微架構改進數量一覽表。

新款 cIOD 整合顯示輸出功能

隨著處理器、平台世代更新,Ryzen 7000 桌上型處理器系列 cIOD 出現不小的變化,包含 DDR5 記憶體和 PCIe 5.0 支援性,USB 也增添 Type-C 支援性和 BIOS Flashback 功能機制,更從 Ryzen 6000 行動處理器系列汲取相關省電性研發成果。

另一方面,熟悉 AMD 處理器的玩家,都知道 Infinity Fabric clock(fclk)、memory controller clock(uclk)、memory clock(mclk)之間的時脈比值最好維持 1:1:1,否則反而會增加傳輸延遲導致效能下降的狀況。Ryzen 7000 系列稍微有些不同,uclk 和 mclk 仍舊建議維持 1:1,但是 fclk 則是建議維持預設值「自動」,記憶體等效時脈甜蜜點為 DDR5-6000,因此不少 EXPO(AMD 版 XMP)記憶體均以 DDR5-6000 作為標準。

▼ Ryzen 7000 系列的 cIOD 有著不小的變化,包含支援 DDR5 記憶體和 PCIe 5.0。

▼ Ryzen 7000 系列的 fclk、uclk、mclk 比值建議為自動:1:1,記憶體等效時脈甜蜜點則是 DDR5-6000。

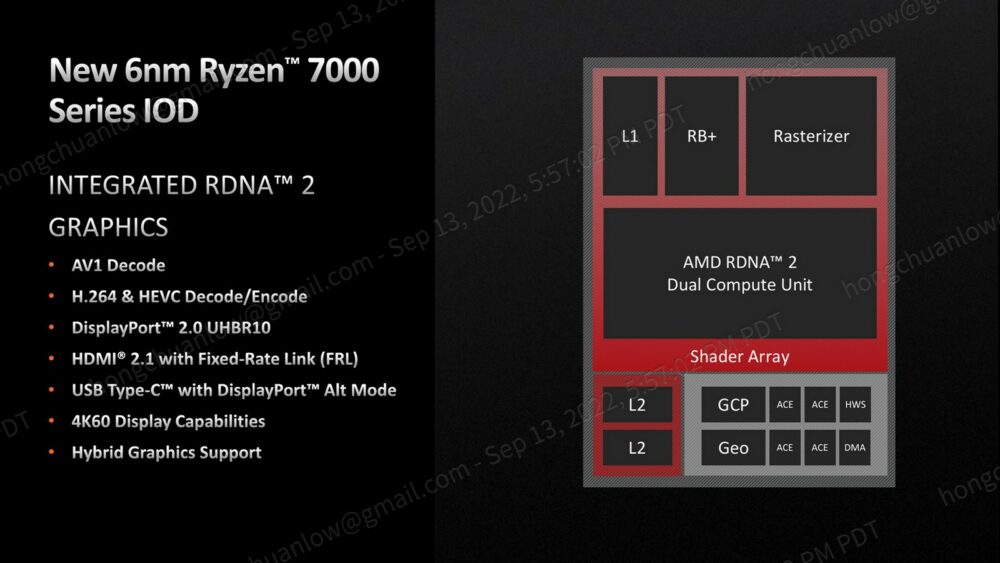

Ryzen 7000 系列 cIOD 最大變動之處,在於整合 RDNA 2 架構的繪圖顯示功能以及影片硬體編解碼加速,雖然只是 2 個 CU 聊勝於無的 3D 效能,但不需要額外加裝獨立顯示卡,即可擁有顯示輸出和多種影片硬體編解碼加速功能,相信對於商用市場有著不小的吸引力。

▼ 受惠於 TSMC N6 製程的電晶體密度表現,Ryzen 7000 系列的 cIOD 整合 RDNA 2 架構繪圖顯示功能,具備 H.264(AVC)/ H.265(HEVC)影片編解碼加速;當額外安裝相容的獨立顯示卡時,也支援 Hybrid Graphics。

▼ Ryzen 7000 桌上型處理器系列內部封裝晶片數量與前代相同,最多能夠封裝 2 個 CCD 和 1 個 cIOD,每個 CCD 對 cIOD 每週期可寫入 16Byte,因此單 CCD 封裝版本(實體8核心以下),執行記憶體頻寬測試時仍有寫入頻寬減半的狀況,但實際應用效能不受影響。

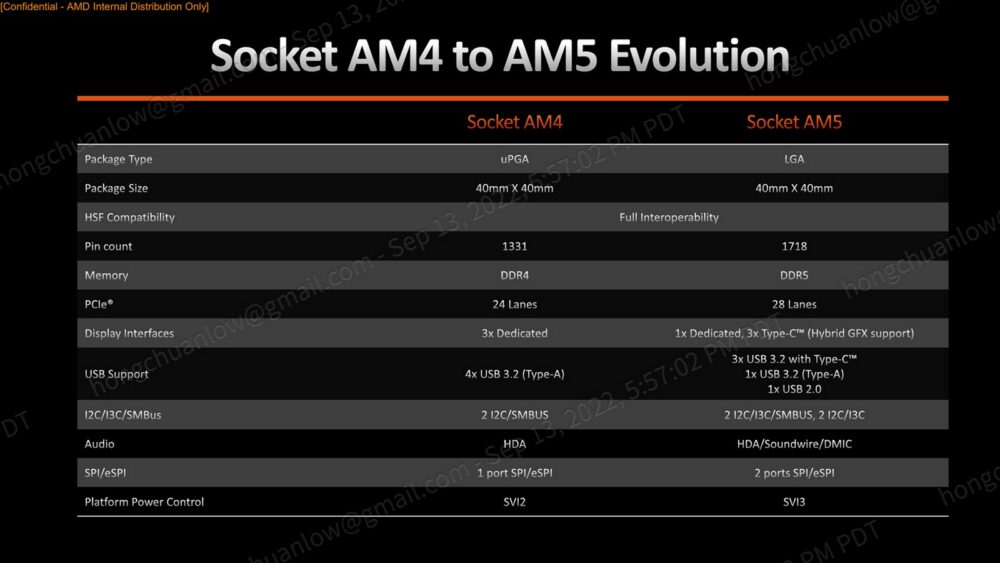

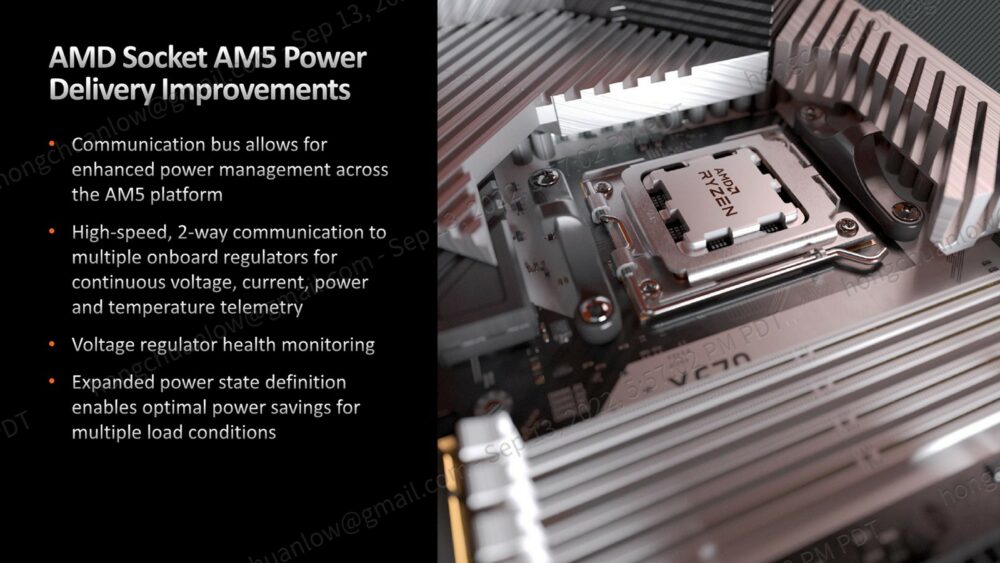

AM5 強化外部供電模組溝通能力

藉由轉換至全新的 AM5 平台,AMD 也連帶改善與週邊的溝通介面,例如新增 I3C,音訊介面也多出 SoundWire 和 DMIC。AMD 特別提到平台電源控制從 SV12 升級至 SV13,支援強化電源管理,高速雙向通訊機制能夠遙測電壓、電流、功耗、溫度、健康度等資訊,並擴展電源狀態定義,迎合最佳化省電管理與不同負載程度下的需求。

▼ AM4 與 AM5 多項重大改善比較。

▼ AM5 平台的電源管理機制將有顯著的改善。

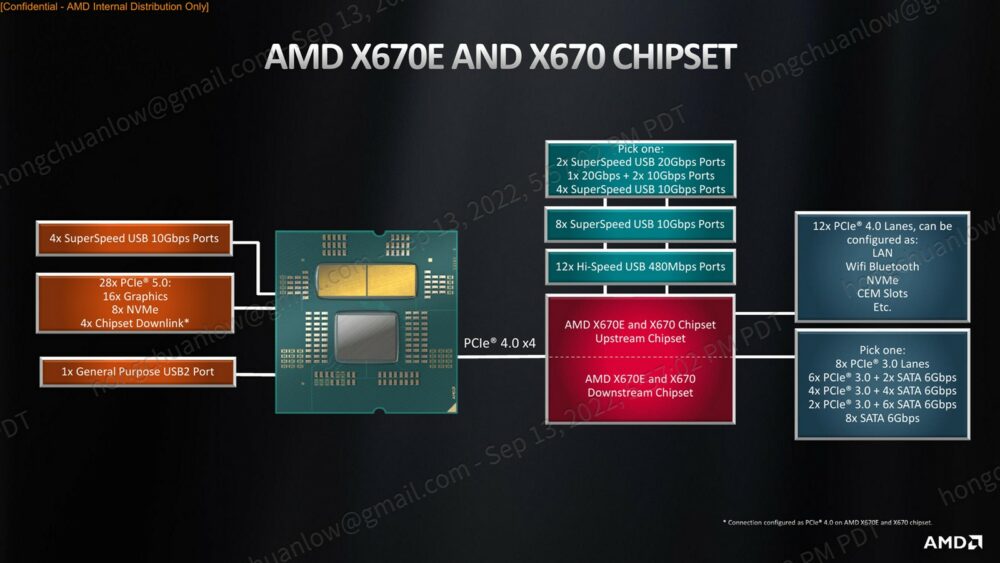

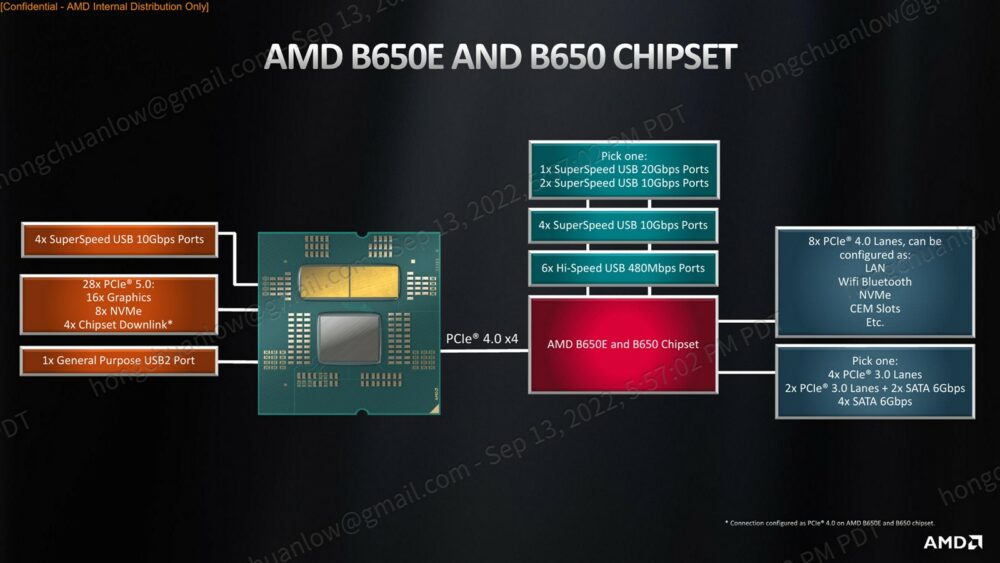

另一方面,這次與 Ryzen 7000 桌上型處理器系列一同推出的 X670 / X670E 和 B650 / B650E 晶片組,除了按照慣例分級之外,X670 / X670E 還能夠以 PCIe 4.0 x4 再串接另外一個 X670 / X670E,達到擴展 I/O 埠的功效。

▼ X670 / X670E 晶片組通道與架構一覽,主機板若要掛名 X670E,AMD 要求顯示卡和 M.2 SSD 插槽均須具備 PCIe 5.0 規格。

▼ B650 / B650E 晶片組通道與架構一覽,主機板若要掛名 B650E,AMD 要求顯示卡和 M.2 SSD 插槽均須具備 PCIe 5.0 規格。

整體而言,這次 AMD 針對 Zen 4 微架構進行的改善工程,與前陣子 Chips and Cheese 網站專題<Measuring Zen 3’s Bottlenecks>專題結論八九不離十,主要是打通 Zen 3 微架構的任督二脈,輔以 TSMC N5 製程所帶來的電晶體密度與時脈紅利,打造 AM5 平台的首代產品 Ryzen 7000 桌上型處理器系列。

在首波產品之後,接著還有透過混合鍵合(hybrid bonding)連接額外 L3 快取晶片,提升 L3 快取容量的 Ryzen 7000 系列 X3D 版本處理器問世。以及推出針對雲端密集運算的 Zen 4c 微架構,最大化每個處理器插槽能夠搭載的核心數量。

▼ AMD Ryzen 7000 系列所有的創新內容一覽。

▼ Zen 微架構逐代改善內容一覽。