近期 Intel 執行長 Bob Swan 大方承認自家 7nm 製程相較原先預計時程延後許多,但於近日舉辦的 Architecture Day 架構日活動當中,該公司仍舊針對目前 10nm 製程電晶體效能不如預期的問題,持續改進並提出多種解方。

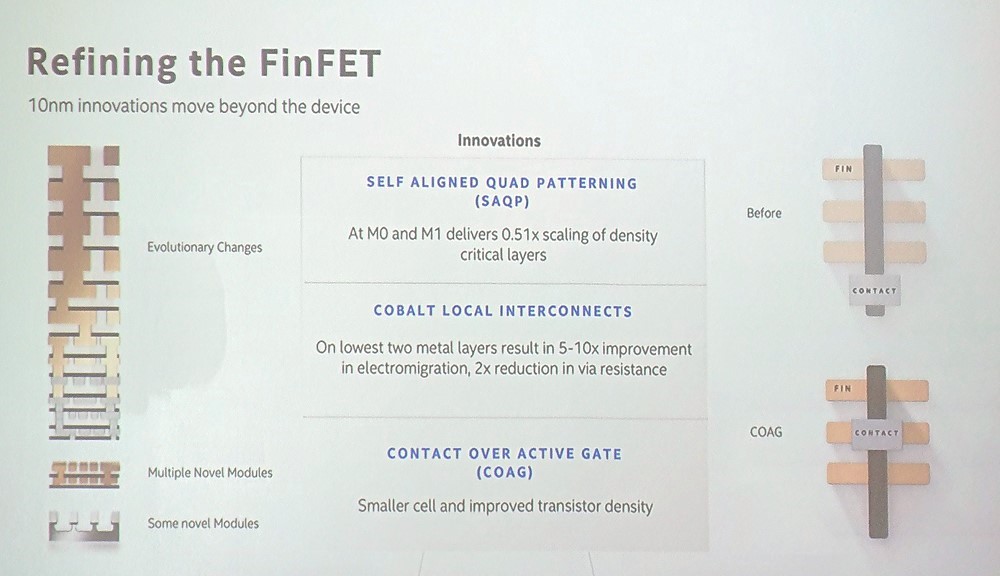

▲Intel 於目前已量產的 10nm 製程(應用於 Ice Lake),導入 SAQP(Self-Aligned Quad Patterning)、CLI(Cobalt Local Interconnects)、COAG(Contact Over Active Gate)等細部改良技術。

▲Intel 於目前已量產的 10nm 製程(應用於 Ice Lake),導入 SAQP(Self-Aligned Quad Patterning)、CLI(Cobalt Local Interconnects)、COAG(Contact Over Active Gate)等細部改良技術。

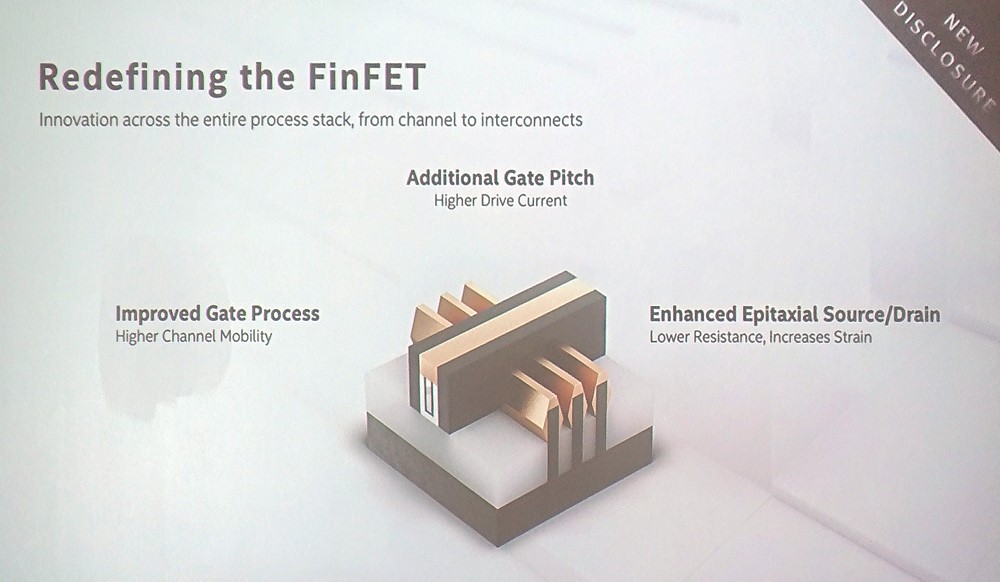

▲SuperFin 超級鰭片式電晶體能夠提升效能表現,代號 Tiger Lake 的第11代行動處理器將是首款應用產品。

▲SuperFin 超級鰭片式電晶體能夠提升效能表現,代號 Tiger Lake 的第11代行動處理器將是首款應用產品。

讓我們從電晶體角度出發,接著再依據製造順序由小至大探討。FinFET 鰭片式電晶體突出於矽基板,就像是矽基板上方長出許多片狀結構,SuperFin 技術強化源極、汲極等磊晶,進而提升應力、縮減電阻、通過更多電流。另一方面同時提供更寬的閘極選項、改善製程,以便提升通道的遷移率,提供更高的驅動電流,對於高效能晶片設計是不可或缺的改進。

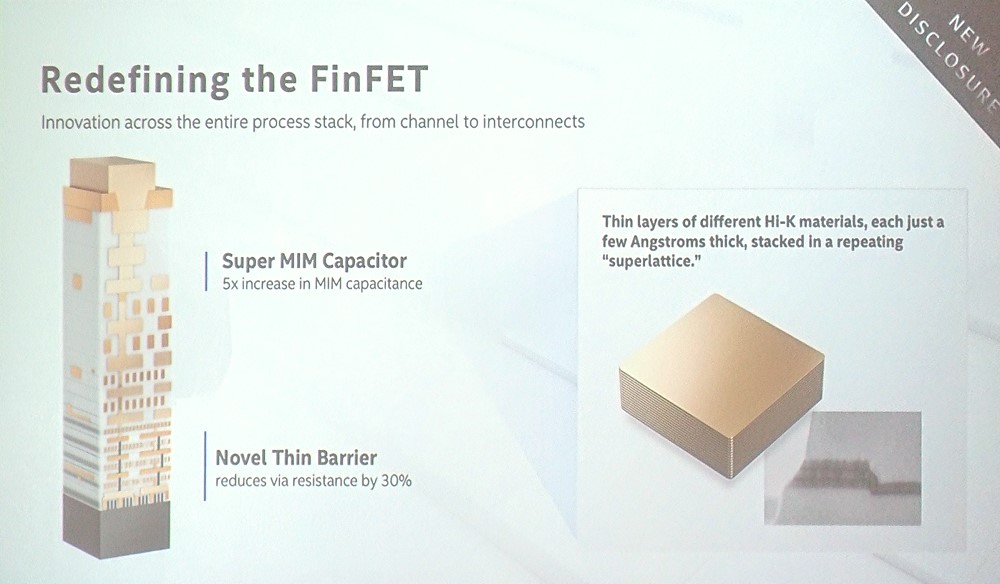

▲接近電晶體的互連層,SuperFin 降低阻障層厚度,降低通孔電阻 30%,上方則是透過 Hi-K 介電材料,於 MIM 當中形成重複的超晶格結構,於占用相同面積的先決條件之下,達成 5 倍電容值。

▲接近電晶體的互連層,SuperFin 降低阻障層厚度,降低通孔電阻 30%,上方則是透過 Hi-K 介電材料,於 MIM 當中形成重複的超晶格結構,於占用相同面積的先決條件之下,達成 5 倍電容值。

在電晶體之上,首先碰觸到電晶體的數層電路,SuperFin 縮減緊鄰線路的阻障層(barrier)厚度,Intel 宣稱能夠減少通孔電阻達 30%。再往上線徑較寬、線距較大的數層電路,內嵌採用 metal-insulator-metal(金屬-絕緣體-金屬)結構的電容,Intel 更進一步採用新型 Hi-K 介電材料,讓佔據相同面積的 MIM 電容,擁有 5 倍的容值,降低電壓驟降(Vdroop)情況,稱之為 Super MIM。

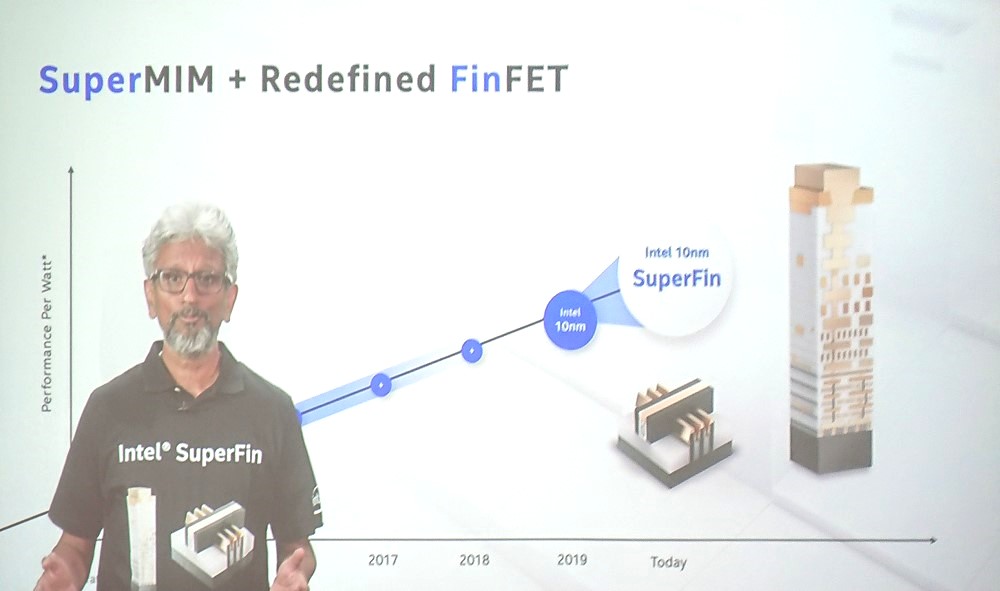

▲Raja Koduri 把 SuperFin 超級鰭片式電晶體穿上身,可見 Intel 內部對於這個節點製程升級多麼重視。

▲Raja Koduri 把 SuperFin 超級鰭片式電晶體穿上身,可見 Intel 內部對於這個節點製程升級多麼重視。

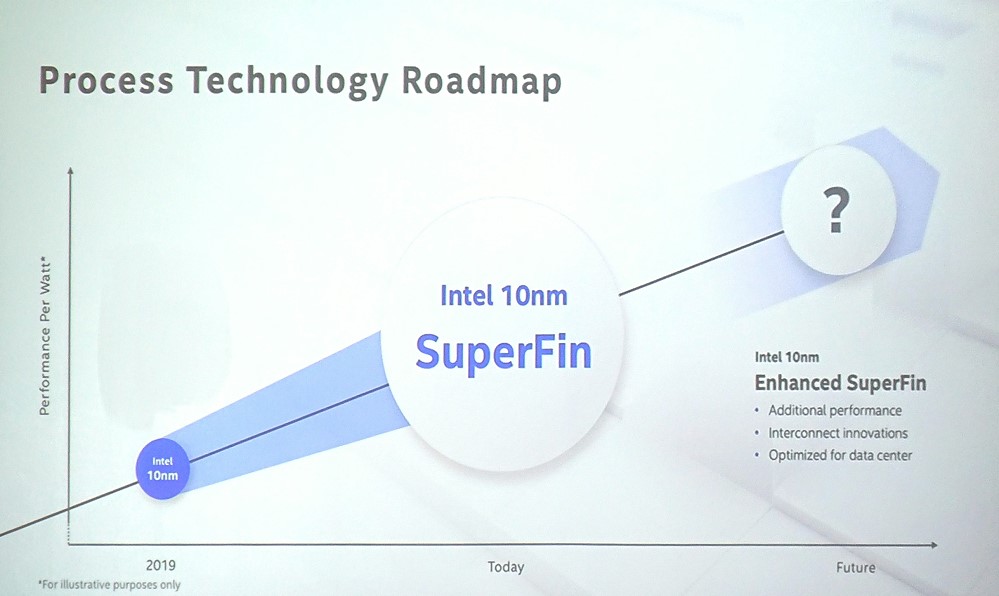

▲10nm 製程除了近日公布的 SuperFin 之外,目前預期還有個 Enhanced SuperFin,詳細資訊尚屬未知,但會提升效能、新款互連改進,並為資料中心最佳化。

▲10nm 製程除了近日公布的 SuperFin 之外,目前預期還有個 Enhanced SuperFin,詳細資訊尚屬未知,但會提升效能、新款互連改進,並為資料中心最佳化。

喔,對了!Intel 未來將拋棄「製程++」這種命名方式,使用在 Tiger Lake 的製程技術稱為 SuperFin,下次使用在 Sapphire Rapids 的製程技術將稱為 Enhanced SuperFin。