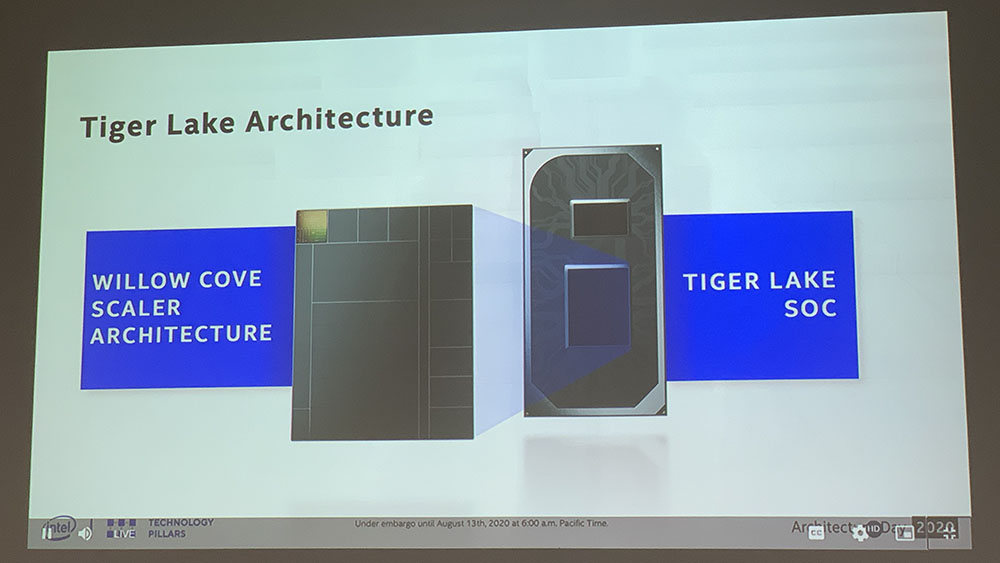

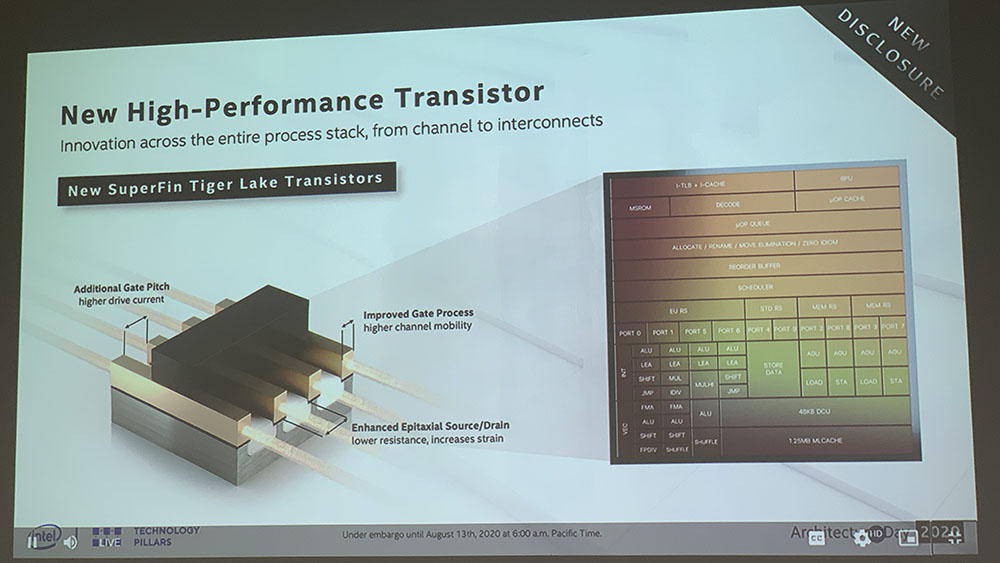

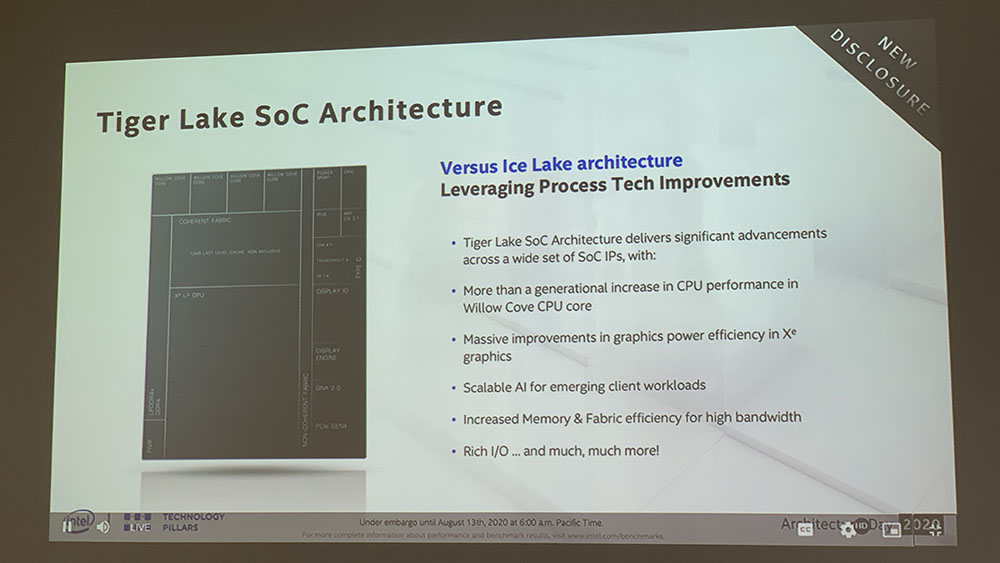

Intel 在 Architecture 2020 活動上,率先揭露採用 Willow Cove 處理器架構的 Tiger Lake 平台的更多資訊與細節;Willow Cove 是 Sunny Cove 之後的第二個 10nm 製程處理器架構,但不同於 Sunny Cove 的部分是,新的 Willow Cove 將導入 Intel 自家的 10nm SuperFin 技術。

除了 10nm SuperFin 技術外,Tiger Lake SoC 同時將導入 Intel 醞釀許久的 Xe-LP GPU 架構,以及整合 Thunderbolt 4 技術。

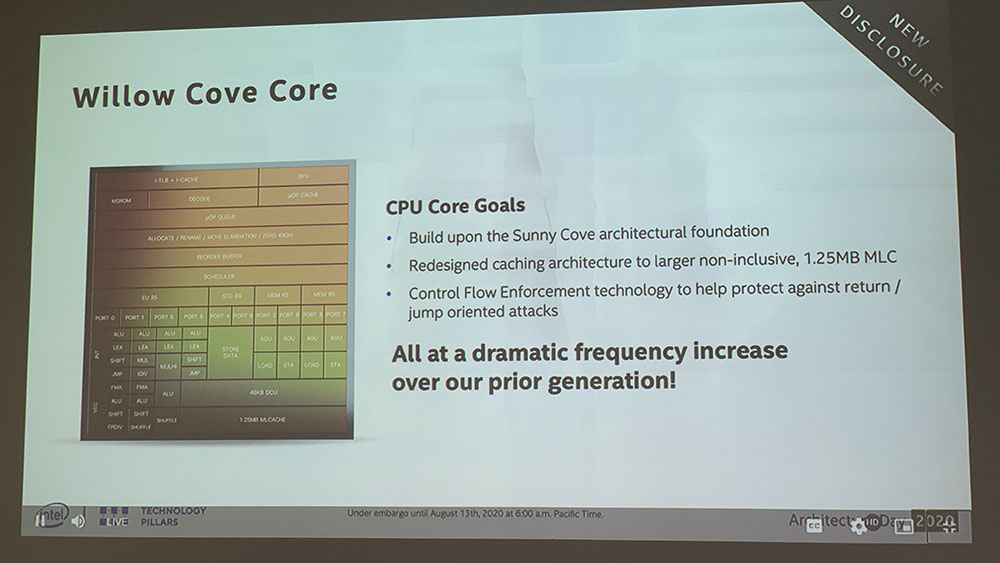

Willow Cove CPU 核心是基於 Sunny Cove CPU 架構上,但 Willow Cove 在 CPU 效能、時脈以及電力方面都有著非常顯著的提升。此外,Willow Cove 更導入了 non-inclusive 1.25MB L2 Cache 這個新的快取架構,也透過 Intel Control-flow Enforcement Technology 增強安全性。

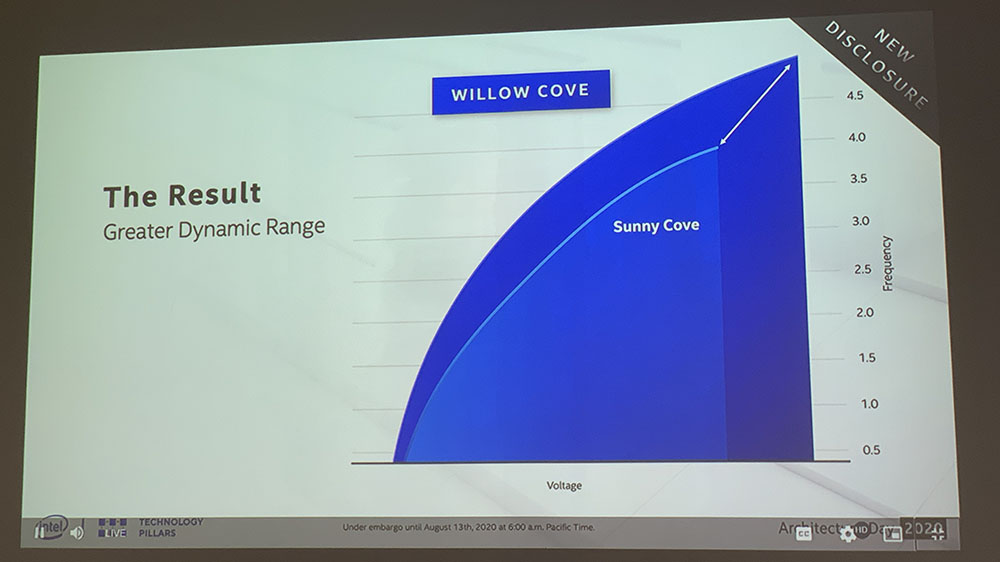

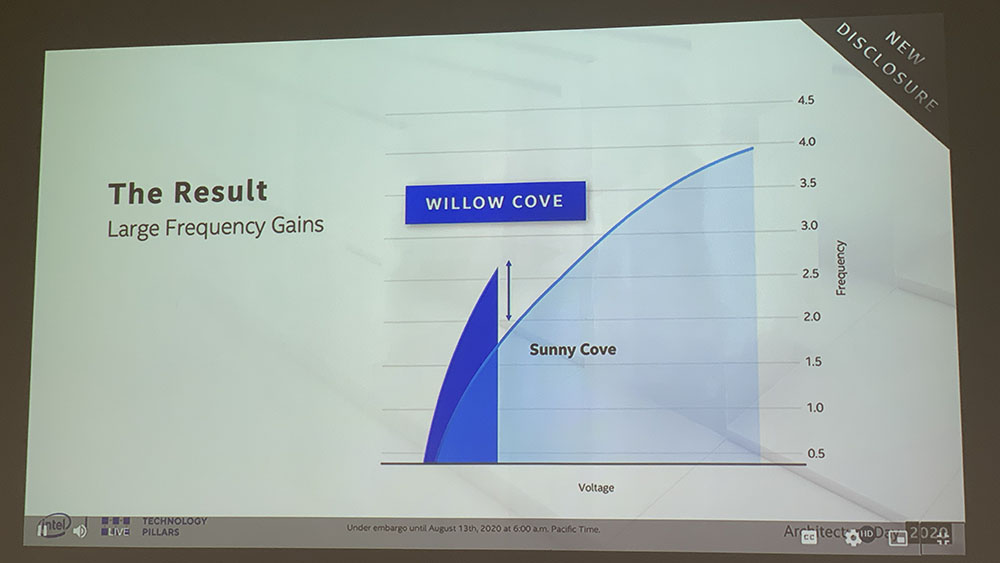

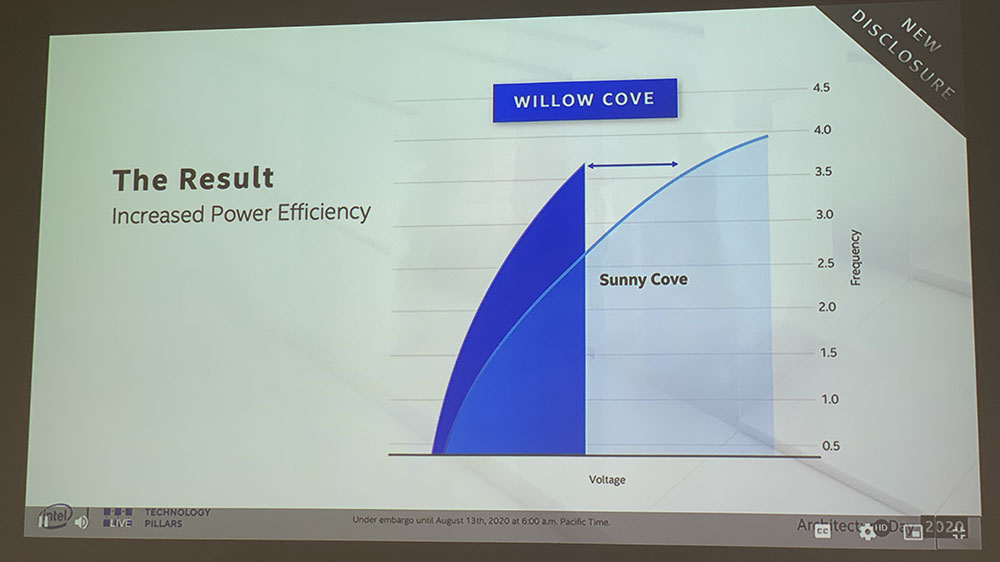

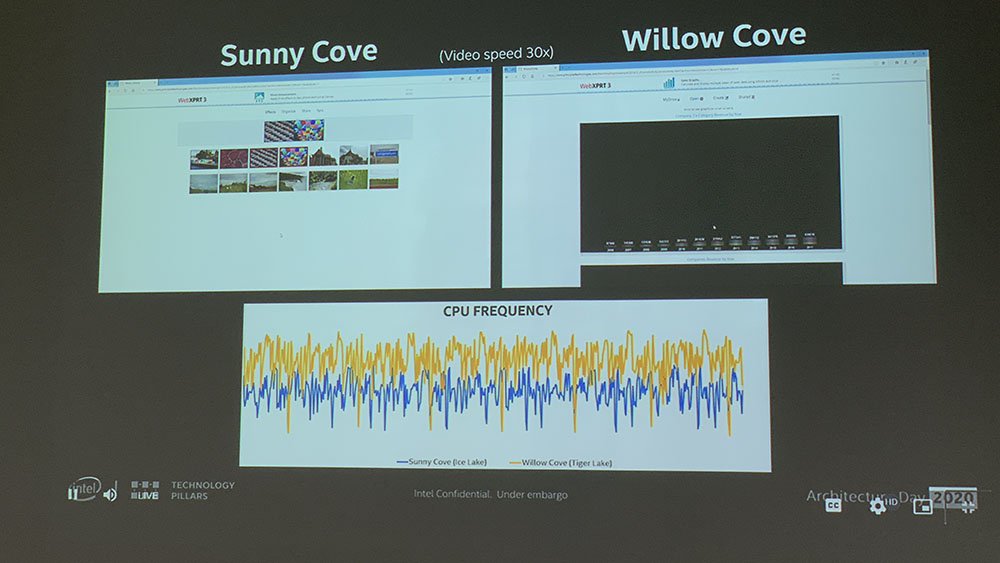

就 Intel 的資料來看,Willow Cove 在 Frequency、Power Efficiency 和 Greater Dynamic Range 這 3 個方面都較 Ice Lake 使用的 Sunny Cove CPU 架構有著相當大的差距。也就意味著,採用 Willow Cove 架構的產品其運作電壓下與 Sunny Cove 相當,但處理器時脈卻能比 Sunny Cove 更高,其功耗要較 Sunny Cove 低。

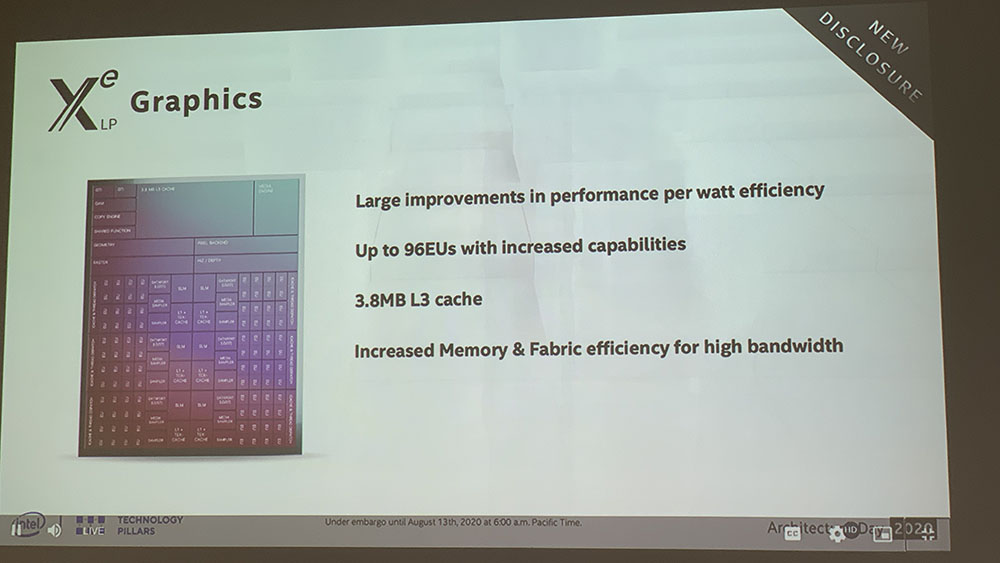

雖然還不確定是否延續過去的 Intel HD Graphics 命名方式,但肯定的 Tiger Lake 平台將全面拋棄過去 Intel 慣用的 iGPU 架構轉換至醞釀許久的 Xe GPU 架構。Tiger Lake 的 Xe GPU 架構最高可以達到 96 EUs,這意味著我們可以透過 Intel 最新的 iGPU 獲得遠超於過去各種 iGPU 的效能表現,套句 AMD 常用的話,那個 Tiger Lake 所使用的 Xe GPU 架構在每瓦效率將有著非常大的突破。

Tiger Lake 平台處理器的 Xe-LP 雖然最高會到達 96 EUs,但這並不表示每一款處理器都如此。

另一方面,也可以注意到 Xe-LP GPU 架構的 L3 Cache 為 3.85MB。

記憶體部分,Tiger Lake 最高可以支援到 LPDDR5-5400MHz,另也可以支援 LPDDR4X-4267MHz 以及標準的 DDR-3200MHz;Ice Lake 平台最高為 LPDDR4-3733MHz 以及 DDR4-3200MHz。DDR4 記憶體部分現階段最高的原生顆粒為 3200MHz,超過這個時脈的產品基本上都是超頻,不屬於 JEDEC 規範。同時,就 Intel 官方的數據,Tiger Lake 平台的記憶體頻寬最高可以達到 86GB/s。

Tiger Lake 的 Coherent Fabric 頻寬也較 Ice Lake 提升了 2 倍。

使用者有望可以透過 Tiger Lake 獲得更佳的視覺效果,這主要是因為 Display 與 IPU6 獲得提升;就 Display 部分,可以見到最高 64GB/s 的同步頻寬(isochronous bandwidth)以及記憶體間的專用架構通道,都是為了確保高解析度畫面與記憶體間的溝通品質,而 IPU6 部分則有多達 6 個感應器用以提供最高 4K90 和 47MP 影像架構相容能力。

功耗部分也會因為 FIVR 效率提高而獲得一定改善,特別是處理器在負載的條件下。

需要注意的還有自主性動態電壓調整(Autonomous DVFS)會在 Coherent Fabric 與記憶體子系統間,基於頻寬而即時對時脈和電壓比例做出改變。

Tiger Lake 的大多資訊介紹完之後,跟著 Intel 確定會在 9 月 3 日晚間正式發表這個採用 10nm SuperFin 製程的平台,如果對這個平台有興趣的話,不妨多做留意。