CCI-550 主打多核心多叢集配置能力強化,下一代 ARM 處理器核心設計方向已可見端倪。

CCI-550 架構主打更多核心叢集配置,看來 ARM 打定主意要在即將發表的新版處理器核心主推MediaTek 首發的 3~4 叢集(Cluster)配置了。

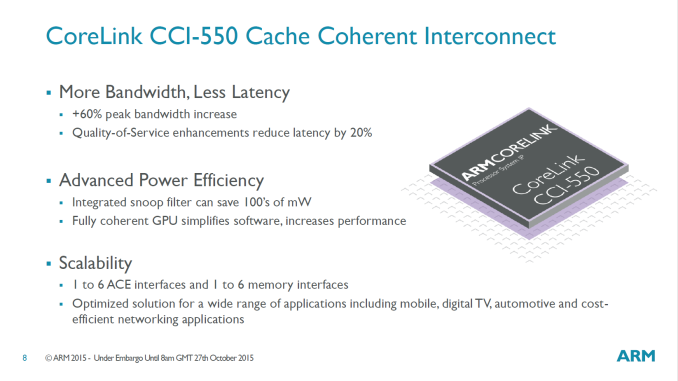

自從今年二月隨著 Cortex-A72 發表 CCI-500 之後,ARM 再接再厲的推出改良版 CCI-550 。

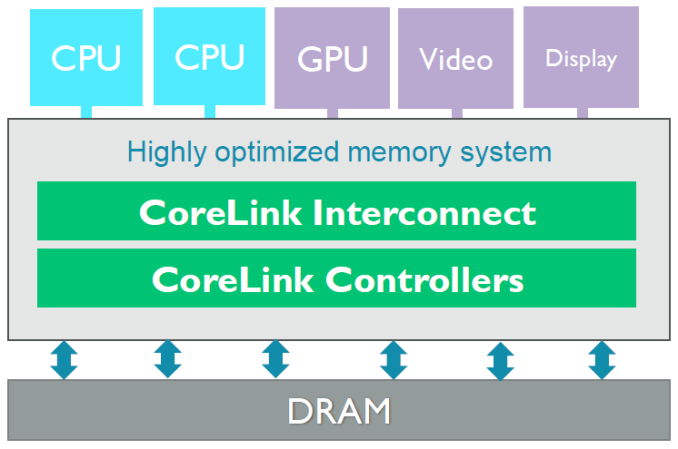

CCI(Cache Coherent Interconnect, 快取一致性互連架構)是整個 ARM SoC 中最重要的部分,不同的 CPU 核心必須透過此互連架構來互相溝通,在發揮最大效能的前提下,還要確保核心之間彼此的暫存資料一致,以免執行出錯。

最新版本的 CCI-550 與 CCI-500 同樣強調增加了由 CCI 端主控的資料探針(Snoop Filter)功能,不必再像舊版本一樣確認時必須喚醒所有的核心,核心會在資料有變更時主動回報本地快取與暫存器中的資料狀態,由 CCI 進行下一次的同步動作,藉由此改進可大幅加快不同核心在資料同步探測時的速度,並降低處理器的功耗。

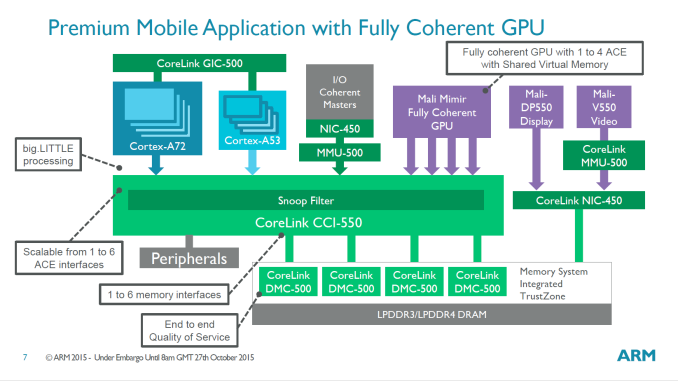

CCI-550 也不是全部都照抄 CCI-500 ,負責資料同步的關鍵處理單元 ACE(AXI Coherency Extension, 先進匯流排同步擴展)的主控連接埠也在不增加核心開銷的前提之下由 4 個增加到 6 個。

由於一個處理器叢集只需要一個 ACE,所以四大四小的配置只需要兩個 ACE,剩下的四個 ACE 可以再分配給 Mali GPU 作為 GPGPU 的資料運算同步或其他開外掛(IMG 表示….)之用,以及,更多的處理器叢集:比如說 MediaTek 的三叢集 Helio X20 與四叢集 Helio X30,都可在CCI-550之下獲得更好的同步效率。

合理推測其實 Helio X20 或 X30 將用上 CCI-550, ARM 與 MediaTek 畢竟關係匪淺,過去 MediaTek 也常是新版 ARM 架構的優先使用者。不過對所有客戶而言,CCI-550 主要還是要用來搭配下一代 ARM 架構核心。

這邊看一下 ARM 一貫的 PPT 大法,CCI-550 不僅支援多達六個記憶體通道,能提供更高的互連頻寬,並降低延遲,當然,等到終端產品出現就能知道真相了。

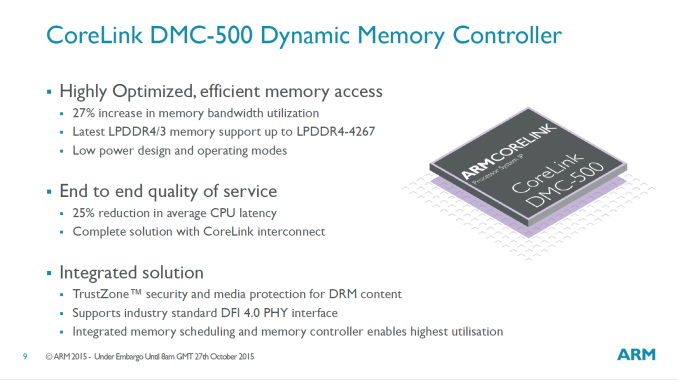

另外,作為 CCI-550 的搭配,ARM 也推出 DMC-500 這個記憶體控制器,強調能支援到 LPDDR4-4667。不過這個控制器的性能不是重點,重點在於這是由 ARM 提供的配套方案,缺乏自有記憶體控制介面技術的廠商,比如說中國 IC 廠商,會很樂見此一方案。