從處理器發展有史以來,不論是我們熟悉的 x86 架構處理器,或者是在手機裡面常見的 SoC,為了增加效能,通常都會藉由堆疊更多處理單元,設計更多管線,或者是增加更多快取記憶體來達成。

但設計處理器就好像針對不同種類運動而鍛鍊身體般,如果僅著眼於強化肌肉,那麼身材、體重也會跟著過度壯碩,雖然可能獲得更大的力量,但消耗的能量也會明顯增加,且運算的型態不只一種,就好比運動的類型也各有不同,舉例來說,過度強化肌肉的訓練,在強調耐力的長跑比賽中,就絕對會吃鱉。

過去處理器的設計,包括 ARM 架構本身,其實多半在為考量支援的應用廣泛性,增加了過多功能與運算單元,導致架構越來越不均衡,雖然在某些狀態下的性能可以獲得改善,但是相對系統需要付出的代價也增加,不論是功耗,或者是整體設計成本。

以ARM為例,ARM 自 Cortex-A15 開始,增加了針對伺服器應用的相關功能,比如說 ECC 記憶體偵錯能力、虛擬化等功能之後,再加上更多的管線階層與更複雜的處理單元設計,製程的進步就開始有追趕不上 ARM 腳步的感覺,比如說,當時最新的 32 / 28nm 製程面對 Cortex-A15,其實在功耗表現上比起前代產品已經有明顯不足的狀況,當然,ARM 為解決功耗上的問題,提出了 big.LITTLE 方案來作為彌補,當時行動應用的負載多半是單純的日常應用程式,遊戲設計也相對簡單,ARM 的作法也確實消除了部分自身架構在某些方面有所不足的問題。

然而 Cortex-A15 之後,ARM 又把同樣的設計思維擺到 Cortex-A57 上,但不巧,製程趕不上 ARM 架構設計理念的狀況又發生了,A57 是個遠比 A15 功能更完整,且更龐大的高效能核心,對系統功耗與溫度控制設計需求更嚴苛,而這次還加上行動終端的遊戲應用開始強調聲光效果,運算負擔也隨之加重的狀況,即便加上 big.LITTLE 設計,面對高負載、且長時間的遊戲運算考驗仍是捉襟見肘,初期便採用 Cortex-A57 的行動方案客戶也因此付出了代價。

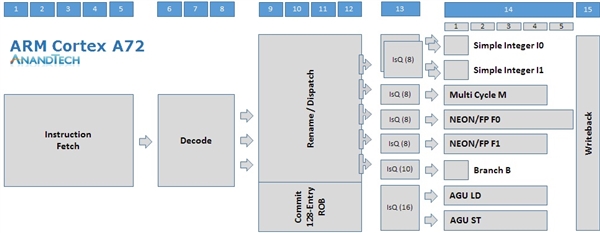

當然,ARM 也快速修正了核心架構發展方向,推出了 Cortex-A72 這個維持 Cortex-A57 架構複雜度,但是在關鍵部分進行精簡與高效化的的設計,舉例來說,A72 相較於 A57,在分支預測的設計上大幅降低了預測失誤率,同時也減少無效的分支預測工作。

另外,管線解碼的性能也得到相當程度的提升,雖然解碼器仍維持 A57 的 3 issue(三道指令)設計,但配合指令集效率的提升,以及增加對應的解碼器頻寬,相關性能也獲得改善,或者是說,同效能表現下,因為處理單元無效動作造成的浪費大幅減少,功耗也得以明顯降低。

雖說犧牲部分高頻效能的延展性,但獲得了更合理的功耗與性能表現,A72 可以說是 ARM 所設計,針對全方位應用的處理器架構中,最具均衡性的一款核心,即便搭配 28nm 製程,也能維持接近、甚至超越舊款旗艦核心的性能輸出,且不會有明顯過熱或耗電的現象,其技術進展不可謂不大。

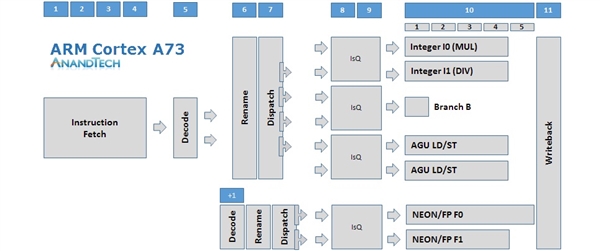

但 ARM 決定更激進的作法,首先,伺服器應用仍僅佔 ARM 營收少數,未來成長空間雖有,但需要時間經營,所以在每代處理器核心都加入伺服器專用的處理單元必要性不大。其次,處理器核心的分支預測、解碼單元以及匯流排和快取設計還有很多可以最佳化的空間,提升性能表現的手段並非只有堆電晶體一途。所以在 Cortex-A73,ARM 決定繼承 Sophia 系列架構,也就是 Cortex-A12 / A17 的設計概念,推出更精簡的最佳化架構,專心打行動應用運算。

Cortex-A73 的設計理念,其實就好比當初 Intel 放棄 NetBurst 架構,轉而以 Core 微架構般,是以精簡、高效率為主要訴求,而不是無限制的追求每單位電晶體運算性能的極致。

然而當年 Sophia 架構似乎不大成功?主要原因並不是因為架構不好,而是因為當初僅支援 32 位元,落後於市場潮流之故。如今在增加了 64 位元的完整支援,以及針對行動應用的情境最佳化之後,架構上的優勢終於可以轉換成應用上的優勢。

A73 相較於 A72 有幾個最主要的設計重點。

首先,就如同 Intel 的 NetBurst 微架構和 Core 微架構的差異,A73 的管線階層要少於 A72,A72 整體管線階層達 15 階,而 A73 僅達 11 階,而在解碼單元的設計上,A73 僅 4 階,而 A72 則是 5 階,而在 Micro OP 數量上, A72 僅 4 個,A73 則是達到 6 個,整數部分增加到 4 個,比 A72 多了一倍。

另外在基本配置設計方面,A73 同樣維持一個叢集(cluster)四核心的設計,但匯流排減少了 AMBA5 CHI 的支援,僅支援 AMBA4 ACE,並且不支援 ECC。

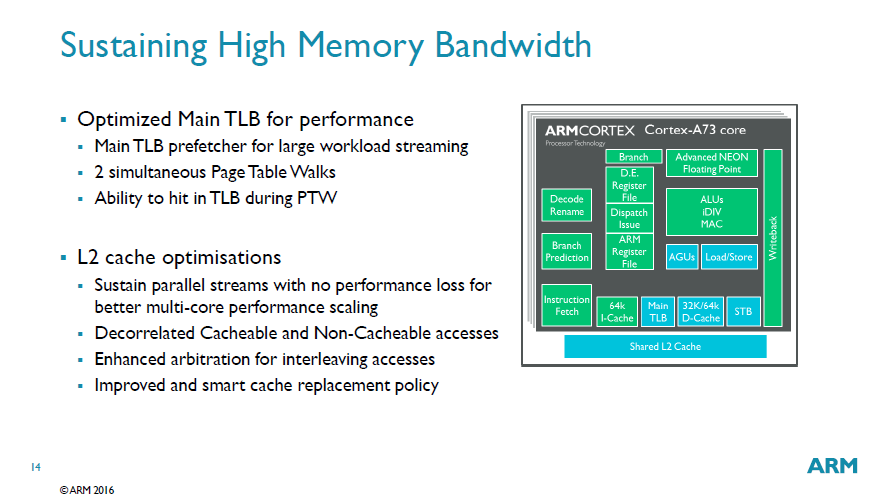

在快取記憶體的設計方面,則是把 PIPT(實體定址實體標籤)更改為 VIPT(虛擬定址實體標籤),並且將 D-CACHE(資料快取)倍增到 64KB,增加資料存取效率,再加上其他改善,整體記憶體頻寬號稱可改善兩成。

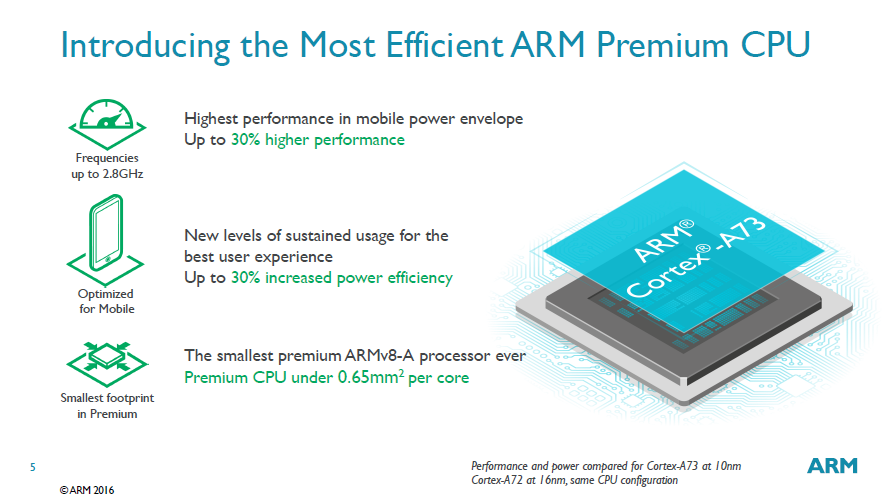

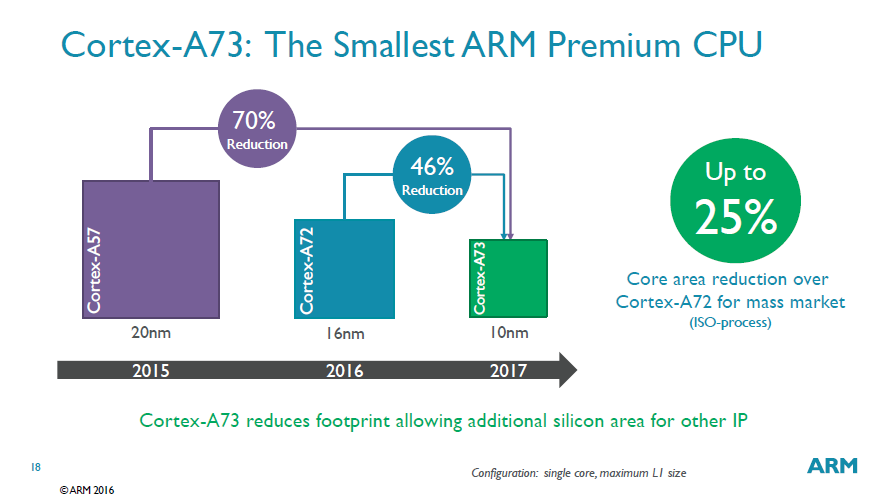

而在製程技術的支援方面,雖然 ARM官方 給的最低規格是 16nm,而最佳製程則是基於 10nm,此時最高時脈可達 3GHz。然而理論上 A73 可在 28nm 輸出可與基於 16nm 的 A72 核心相提並論的性能與功耗表現,未來製程成本越來越高昂,為避免僅剩少數大廠可以享受新架構帶來的優勢,降低製程門檻,增加既有客戶導入新架構意願也同樣是 ARM 所努力的方向。

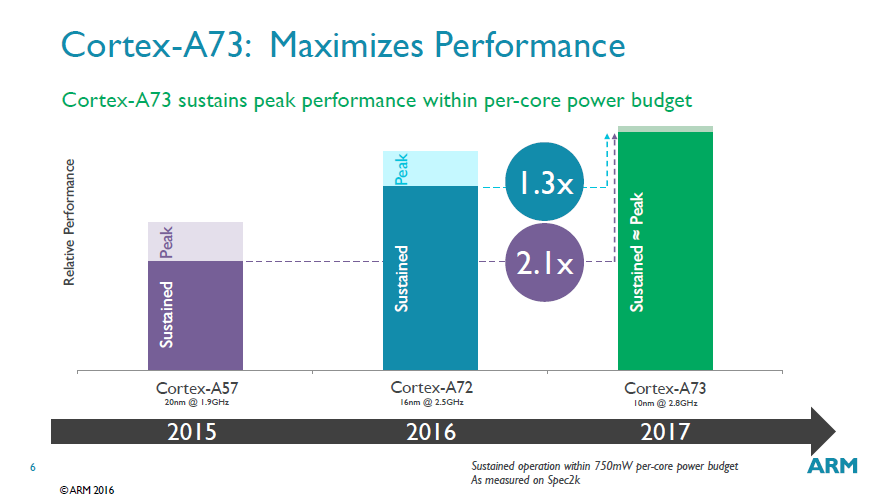

而 ARM 這次產品發表中所一直強調,可穩定持續的高負載運算性能輸出,其實就是在架構精簡,但相關演算單元經過高度最佳化之後的表現,由於非必要的電晶體數量已經大幅減少,藉此同時降低動態功耗與靜態功耗之後的整體性能改善。

當然,ARM 在 Cortex-A73 這個世代放棄了許多伺服器相關功能,並不代表 ARM 放棄了伺服器應用領域。雖然 Cortex-A73 為了追求能源效率,在 IPC(Instruction Per Clock cycle)的設定就放得鬆些,減少管線階層、不追求極限的時脈表現,轉而將架構設計目標定位在均衡、持久。但其實這些設計概念,或部分針對處理運算的細節最佳化都還是可以回饋到將來伺服器處理器的架構設計上。

另外,ARM 提供的各種授權機制也讓客戶能夠針對不同應用配置、甚至自行設計出合宜的應用架構,事實上,目前多數採用 ARM 架構設計伺服器晶片的廠商多是採用指令集授權,自行設計完整晶片,也因此,ARM 在此其實推公版設計的意義相對較小,但是對於希望引進高效能架構,卻缺乏研發資金與相關人才的企業,尤其針對是變化性較高的行動運算產業而言,公版 ARM 架構對產業可說扮演著關鍵角色。